### **Features**

- Voice Recorder/Player on a Chip

- On-board Flash Memory

- Low Voltage and Low Power Operation

- 2.4V to 3.3V

- 10 mA Active I<sub>CC</sub> Current

- 0.1 μA Standby I<sub>CC</sub> Current

# **Description**

The AT72AV010 is a single-chip voice recorder/player with on-board nonvolatile memory. Output from a microphone is processed on-chip and stored in digital form in memory. Data from the memory is then processed and presented to a speaker for playback. Up to 20 seconds of voice can be stored in the 1-Mbit Flash memory at the nominal sampling frequency of 6.4 kHz. The device is available in a space saving 8-lead Leadless Array Package (LAP).

**Pin Configuration**

| Pin Name | Function            |  |

|----------|---------------------|--|

| MIC1     | Ndiananhana lanasta |  |

| MIC2     | Microphone Inputs   |  |

| GND      | Ground              |  |

| VCC      | Power Supply        |  |

| SPK1     | Charles Outputa     |  |

| SPK2     | Speaker Outputs     |  |

| PLAY     | Combrellanista      |  |

| RECORD   | Control Inputs      |  |

#### 8-lead Leadless Array Bottom View

Voice Recorder/Player IC

AT72AV010

Preliminary Information

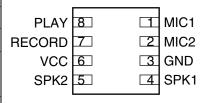

# **Block Diagram**

# Device Operation

After connecting a microphone to the MIC1 and MIC2 inputs and a speaker to the SPK1 and SPK2 outputs, operation of the voice recorder is controlled by the PLAY and RECORD inputs.

With both PLAY and RECORD low, the AT72AV010 is in standby mode. Both control pins have on-chip pull-downs; i.e., they are normally low, unless pulled up to  $V_{CC}$  by external switches.

Taking PLAY high, while RECORD stays low starts playback. Playback continues either until the end of memory or until encountering empty memory.

A recording session is started by pulsing RECORD high, while PLAY is high. Following the low-to-high transition of RECORD, the entire memory is erased. Completion of the internally timed chip erase operation is signaled to the user by a short beep played through the speaker. Recording starts after the beep and continues until the entire memory is filled or until PLAY is taken low. If end of memory is reached during recording, then the beep is played again; signaling to the user that recording has stopped.

Recording can be initiated either during playback or after playback. Nevertheless, while waiting for a RECORD command, the device will draw more current than in standby and therefore PLAY should be taken low if no recording is imminent; this will save battery life.

To play back a fresh recording, PLAY must first be taken low and then high again.

Both PLAY and RECORD inputs are internally debounced for approximately 80 ms to avoid false command triggering. If RECORD is high while PLAY is low, the AT72AV010 enters a Direct Memory Access (DMA) mode; therefore this condition should be avoided in voice recorder (or player) applications; i.e., RECORD should be pulsed high only while PLAY is high.

# **Absolute Maximum Ratings\***

| Operating Temperature                     | 0°C to +70°C   |

|-------------------------------------------|----------------|

| Storage Temperature                       | 65°C to +150°C |

| Voltage on Any Pin with Respect to Ground | 1.0V to +4.0V  |

| Maximum Operating Voltage                 | 3.6V           |

| DC Output Current                         | 50 mA          |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Pin Capacitance<sup>(1)</sup>

| Symbol           | Parameter                       | Max | Units | Conditions           |

|------------------|---------------------------------|-----|-------|----------------------|

| C <sub>I/O</sub> | Input/Output Capactitance (SPK) | 8   | pF    | $V_{I/O} = V_{CC}/2$ |

| C <sub>IN</sub>  | Input Capacitance (MIC)         | 6   | pF    | $V_{I/O} = VG$       |

Note: 1. This parameter is characterized and is not 100% tested.

## **DC Characteristics**

$V_{\text{CC}}$  = 2.4V to 3.3V  $T_{\text{A}}$  = 0°C - 70°C unless otherwise noted.

| Symbol            | Parameter       | Condition                             | Min | Тур  | Max  | Unit |

|-------------------|-----------------|---------------------------------------|-----|------|------|------|

| V <sub>CC</sub>   | Supply Voltage  |                                       | 2.4 |      | 3.3  | V    |

| I <sub>REC</sub>  | Supply Current  | Recording @ $V_{CC} = 3.3V$           |     |      | 10.0 | mA   |

| I <sub>PLY</sub>  | Supply Current  | Playing @ $V_{CC} = 3.3V$ (No Load)   |     |      | 10.0 | mA   |

| I <sub>S</sub>    | Standby Current | Play and Record Low                   |     | 0.1  |      | μΑ   |

| I <sub>SINK</sub> | Input Sink      | On Play/Record Pins @ V <sub>CC</sub> |     | 30.0 |      | μΑ   |

### **AC Characteristics**

$V_{CC}$  = 2.4V to 3.3V  $T_A$  = 0°C - 70°C unless otherwise noted.

| Symbol                           | Parameter                                | Condition                | Min  | Тур | Max  | Unit            |

|----------------------------------|------------------------------------------|--------------------------|------|-----|------|-----------------|

| f <sub>S</sub>                   | Sampling Frequency <sup>(1)</sup>        |                          | 5.8  | 6.4 | 7    | kHz             |

| BW                               | Bandwidth <sup>(1)</sup>                 | f <sub>S</sub> = 6.4     |      |     | 2.7  | kHz             |

| $\Delta f_{\rm S}$ / $f_{\rm S}$ | f <sub>S</sub> Stability <sup>(1)</sup>  | $V_{CC} = 2.7V \pm .3V$  |      |     | ± 3  | %               |

| R <sub>MIC</sub>                 | Input Impedance <sup>(2)</sup>           | to VG                    |      | 60  |      | kΩ              |

| A <sub>VREC</sub>                | Recording Gain <sup>(3)</sup>            |                          | 17.5 | 28  | 38.5 | dB              |

| A <sub>VPLY</sub>                | Playback Gain <sup>(3)</sup>             |                          | 4    |     | 7    |                 |

| V <sub>OMPP</sub>                | Maximum Output Voltage <sup>(3)</sup>    | Matching V <sub>CC</sub> | 3.2  |     | 5.6  | V <sub>PP</sub> |

| I <sub>OMP</sub>                 | Maximum Output Current <sup>(3)</sup>    |                          | 35   | 40  | 45   | mA              |

| V <sub>OS</sub>                  | Output Offset <sup>(4)</sup>             |                          |      |     | 100  | mV              |

| T <sub>HD</sub>                  | Total Harmonic Distortion <sup>(5)</sup> | @ 1 kHz                  |      | 1   |      | %               |

Notes:

- 1. Sampling frequency is set at the factory to 6.4 kHz. Upper pass band limit tracks the sampling frequency, while the lower limit is determined by the time constant of the microphone connection, typically in the 100 200 Hz range.

- 2. The quiescent level of the MIC inputs is at virtual ground (VG). The VG is a level between GND and  $V_{CC}$ . The DC resistance between the MIC input and VG is typically 60 k $\Omega$ . The external microphone should be AC-coupled to the MIC input with 0.1  $\mu$ F ceramic capacitors.

- 3. Recording gain is factory adjusted. The nominal recording gain is 28 dB, i.e., an Input signal of 32 mV<sub>PP</sub> is amplified to the internal full scale voltage of 800 mV<sub>PP</sub>. The gain can be adjusted up or down in steps of 1.5 dB, from a minimum gain of 17.5 dB to a maximum gain of 38.5 dB. Playback gain is also factory adjusted. The power amplifier amplifies the internal signal by 4, 5, 6 or 7. The quiescent output level is approximately halfway between GND and V<sub>CC</sub>. To avoid clipping, the maximum output signal should be matched to the low end of the expected V<sub>CC</sub> range. The recommended speaker impedance is 200Ω.

- 4. Output offset is measured by playing back a recorded input "short."

- 5. THD is typically better at lower recording gain.

#### **DMA Mode**

A Direct Memory Access (DMA) mode is provided for test and development purposes.

The DMA mode is activated by taking the M1 (RECORD) input high, while keeping M0 (PLAY) low. This mode provides access to the internal Flash memory as well as to the parameter configuration register; therefore, the DMA mode should only be used after first consulting with the factory.

In DMA mode it is possible to digitally record pre-processed data which can then be played back through the speaker.

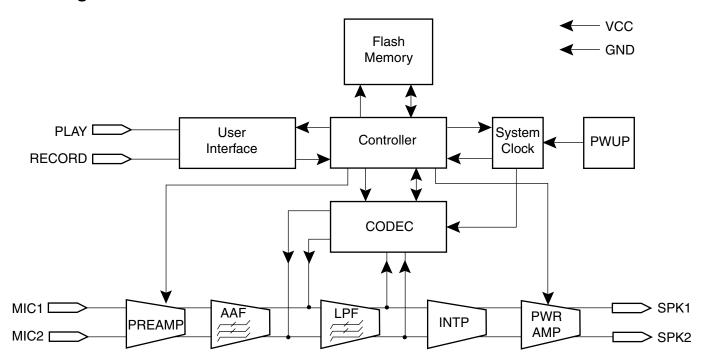

# **Pin Configuration in DMA Mode**

| Pin Name | Function            |

|----------|---------------------|

| SI       | Serial Data Input   |

| CS       | Chip Select         |

| SO       | Serial Data Out     |

| SCK      | Serial Data Clock   |

| VPP      | High Voltage Supply |

| MRGV     | Factory Use         |

| МО       | ,                   |

| M1       | Control Inputs      |

| NC       | Not Connected       |

| Cerdip     |    |    |            |  |  |

|------------|----|----|------------|--|--|

| Top View   |    |    |            |  |  |

| NC□        | 1  | 20 | □NC        |  |  |

| NC□        | 2  | 19 | □NC        |  |  |

| MIC1/SI □  | 3  | 18 | □PLAY/M0   |  |  |

| MIC2/SCK □ | 4  | 17 | □RECORD/M1 |  |  |

| VPP□       | 5  | 16 | ⊐MRGV      |  |  |

| NC□        | 6  | 15 | □NC        |  |  |

| GND□       | 7  | 14 | □vcc       |  |  |

| GND□       | 8  | 13 | □vcc       |  |  |

| SPK1/SO□   | 9  | 12 | □SPK2/CS   |  |  |

| SPK1/SO□   | 10 | 11 | □SPK2/CS   |  |  |

|            |    |    |            |  |  |

In DMA mode the 1-Mbit Flash memory can be erased, written and read by using SPI protocol type commands. Internal parameters such as pre-amp and power-amp gain, as well as sampling frequency can also be modified in DMA mode. Consult factory for details.

The two additional pins presented in the 20-pin Cerdip package are ignored in Audio mode; therefore, the 20-pin package can be used for development of Audio applications (as sockets are more readily available). A 12V supply is needed on VPP; this pin should not be connected in Audio applications. The MRGV pin is used in production for Margin testing and should not be connected in Audio applications. The DMA mode can be used in the 8-lead LAP as well, but write speed is 8 times slower in the absence of a high voltage on VPP.

# **Bonding Information**

Die Size: 3.6 x 3.9 mm

# **Packaging Information**

# 8C1 - LAP

Dimensions in Millimeters and (Inches)\* \*Controlling Dimension: Millimeters SIDE **TOP VIEW VIEW** 5.10 (0.201) 4.90 (0.193) 1.14 (0.045) 8.10 (0.319) 0.94 (0.037) 7.90 (0.311) 0.38 (0.015) **BOTTOM VIEW** 0.30 (0.012) 1.32 (0.052) 1.22 (0.048) 1.22 (0.048) 1.12 (0.044) 0.95 (0.037) 0.85 (0.033) 4.76 (0.187) 4.66 (0.183) 0.92 (0.036) 0.34 (0.013) 0.82 (0.032) 0.24 (0.009)

| 4Imei   | 2325 Orchard | Parkway |

|---------|--------------|---------|

| AIIIIEL | San Jose, CA | 95131   |

| TITLE                                           |       |

|-------------------------------------------------|-------|

| 8C1, 8-lead 0.300" Wide, Leadless Array Package | (LAP) |

| DRAWING NO. | REV. |

|-------------|------|

| 8C1         | Α    |

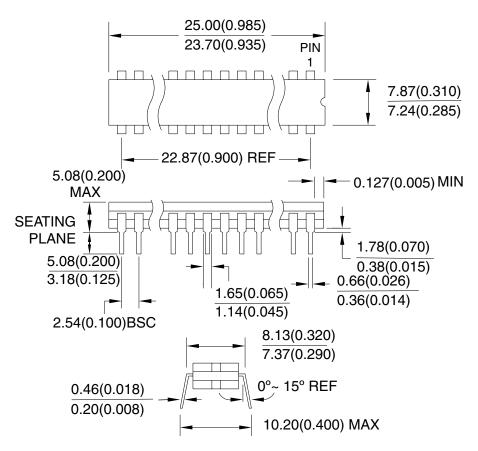

### 20D3 - Cerdip

Dimensions in Millimeters and (Inches)\*

MIL-STD-1835 D-8 CONFIG A (Glass-Sealed)

\*Controlling Dimension: Inches

04/11/2001

REV.

2325 Orchard Parkway San Jose, CA 95131 **TITLE 20D3**, 20-lead, 0.300" Wide. Non-windowed, Ceramic Dual Inline Package (Cerdip)

DRAWING NO. 20D3

3 A

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### **Atmel Smart Card ICs**

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

e-mail literature@atmel.com

Web Site http://www.atmel.com

*BBS* 1-(408) 436-4309

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.