# circuit designs

3 Collected Circards

# PWilliams/JCarruthers/JHEvans/JKinsler

A WIRELESS WORLD PUBLICATION

THIS BOOK is for those who design, use or understand electronic circuits. It contains the information previously included on sets 21 to 30 of Circards, corrected where necessary, and supplemented with ten pages of new circuits. Introductory articles originally published in Wireless World complement each section.

In October 1972, Wireless World launched a circuit information system called Circards. The system was based on issued sets of 8×5 in cards suitable for personal filing systems. Published in conjunction with introductory articles in Wireless World, Circards gave the subscriber descriptions of circuit operation, component values and ranges, circuit limitations and modifications, performance data and graphs.

Circuit Designs No.1 and No.2, containing information on Sets 1 to 10 and 11 to 20 respectively, are now out of print. However, sets of cards are still available at £2 per set, supplied post free in plastic wallets.

# circuit designs

**Collected Circards**

PWilliams/JCarruthers/JH Evans/JKinsler Paisley College of Technology, Renfrewshire

A WIRELESS WORLD PUBLICATION LONDON IPC BUSINESS PRESS LTD

All rights reserved. No part of this publication may be reproduced in any form without permission.

© 1978 IPC Business Press Ltd.

First published as Wireless World Circards in card format by IPC Electrical-Electronic Press Ltd.,

Dorset House, Stamford Street, London, SE1 9LU,

England, a subsidiary of IPC Business Press Ltd.

Introductory articles were first published in Wireless World.

Edited by Geoffrey Shorter, technical editor,

Wireless World.

Publishing Director: Gordon Henderson

IPC Electrical-Electronic Press Ltd.

Printed and bound in Great Britain by Chapel River Press, Andover, Hants.

ISBN 0 617 00241 X

| ACCESSION No. 131914 X |     |          |     |

|------------------------|-----|----------|-----|

| UNIASS No.             |     |          |     |

| <u>(</u> -             |     |          | CIR |

| 3 6AUG 1979            |     |          |     |

| ∪,S                    | IV. | CATEGORY |     |

| · ·                    |     | N        |     |

#### Contents

#### Preface page 5

# Set 21: Voltage-to-frequency converters page 7

Background article/v-to-f converter using unijunction/multiplier converter/delta-sigma converter/sinewave converters/multiphase converter/monolithic i.c. converters/unijunction converter linearized/linear types/diode pump converter/converter with differential input/up-date circuits

#### Set 22: Amplitude modulators page 21

Background article/i.c. package modulators/linear modulator/modulator using precision rectifiers/modulated crystal oscillator/diode bridge modulators/s.s.b. generation/f.e.t. modulators/long-tailed pair modulators/micropower a.m./direct tuned-circuit modulator/up-date circuits

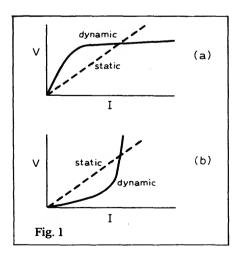

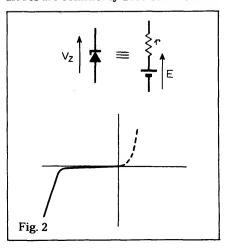

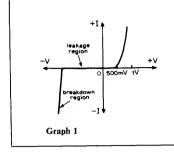

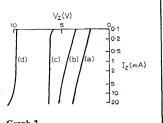

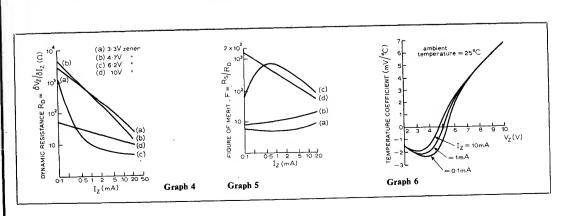

#### Set 23: Reference circuits page 35

Background article/zener diode characteristics/Williams ring-of-two reference/variable reference diodes/bipolar references/low temperature coefficient voltage references/ $\mu$ A-mA and mV-V calibrator/non-zener device characteristics/compensated reference circuits/simple current reference/monolithic i.c. reference/up-date circuits

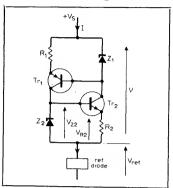

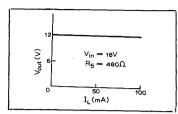

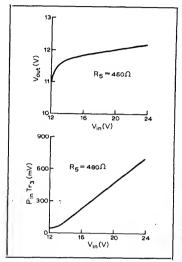

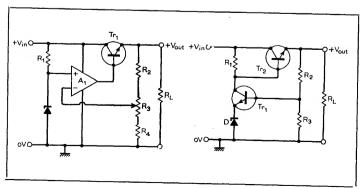

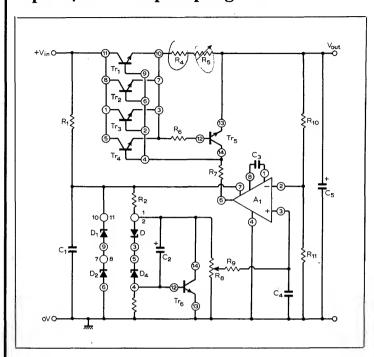

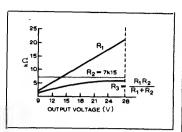

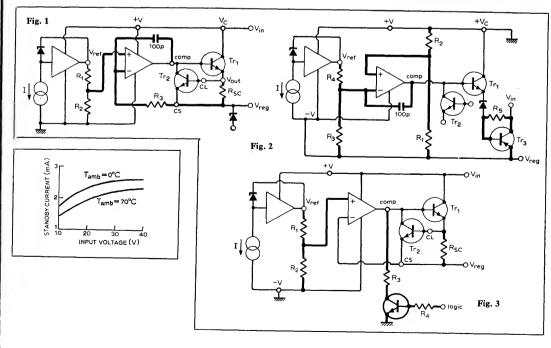

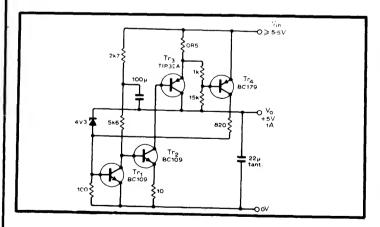

#### Set 24: Voltage regulators page 49

Background article/zener diode shunt regulator/simple transistor regulators/feedback series regulators/bipolar-m.o.s. op-amp regulator/monolithic i.c. regulators—1/ monolithic i.c. regulators—2/voltage regulation using current differencing amplifiers/dual-polarity circuit/switching regulator/self-regulating d.c.-d.c. converter/up-date circuits

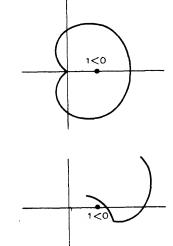

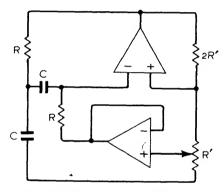

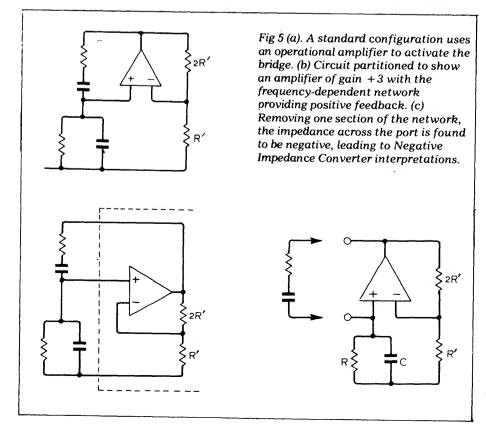

# Set 25: RC oscillators- I page 63

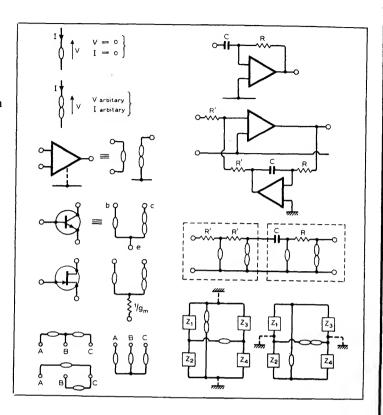

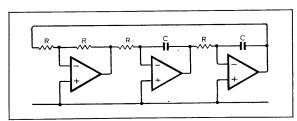

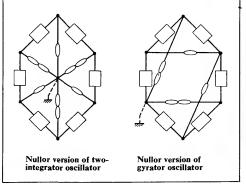

Background article/nullors, networks and n.i.cs/current-driven Wien oscillator/voltage-current Wien circuit/op-amp Wien oscillator/micropower circuit/amplitude control methods/Baxandall RC oscillator/oscillators using n.i.cs/single-element oscillators—1/single-element oscillators—2/up-date circuits

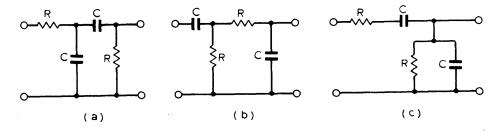

#### Set 26: RC oscillators- Il page 78

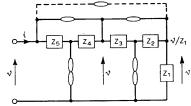

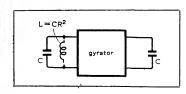

Passive and active networks/parallel-T oscillators/phase shift circuits/f.e.t. phase shift oscillators/oscillator using current differencing amplifier/four-phase oscillator/oscillator using all-pass network/gyrator circuits/wide-range gyrator oscillator/up-date circuits.

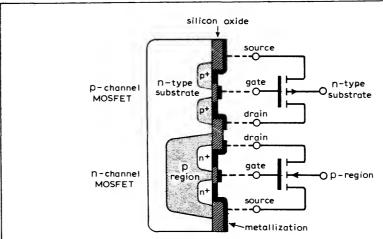

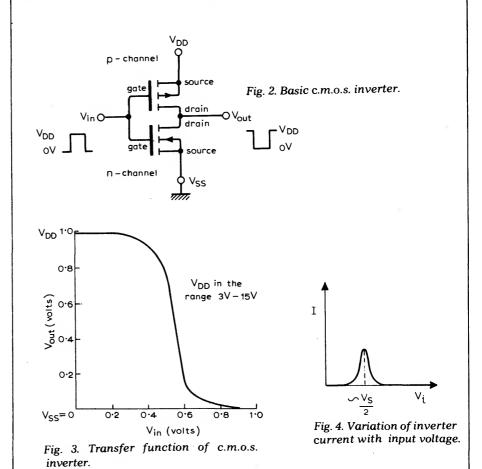

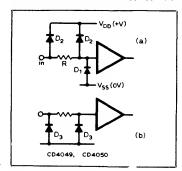

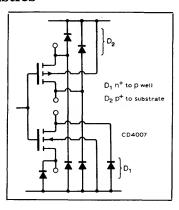

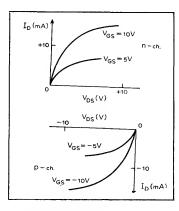

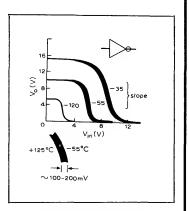

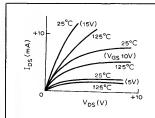

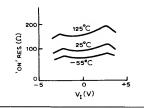

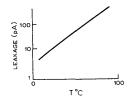

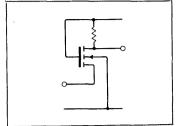

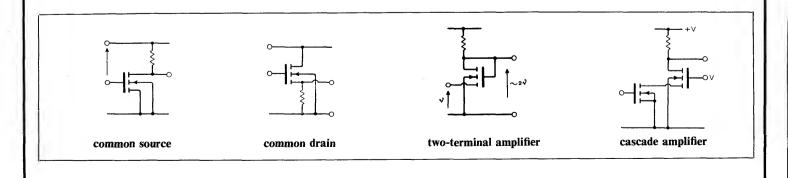

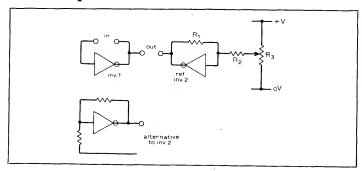

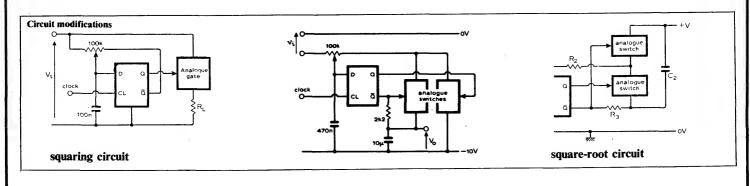

#### Set 27: c.m.o.s.-1 page 89

Background article/linear c.m.o.s. circuits/devices and characteristics/linear circuit characteristics/de ice configurations/d.c. amplifiers/a.c. amplifiers/gain-controlled amplifiers/controlled resistances/non-linear circuits—1/non-linear circuits—2/square-triangle generator/up-date circuits.

# Set 28: c.m.o.s.- II page 103

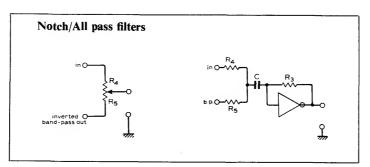

D.C. feedback pair/low-pass, high-pass filters/band-pass, notch filters/D-type analogue circuits—1/D-type analogue circuits—2/three-phase oscillator/frequency to voltage converter/two-integrator oscillator/current-differencing amplifier/ transistor outputs/up-date circuits.

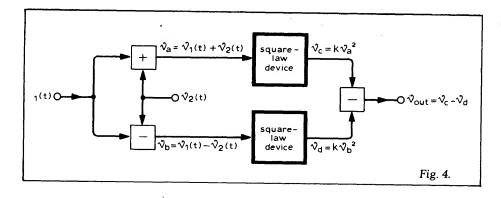

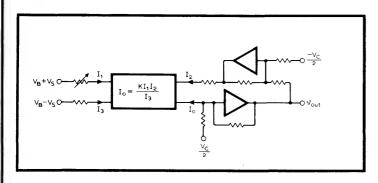

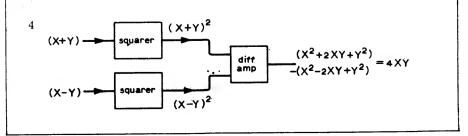

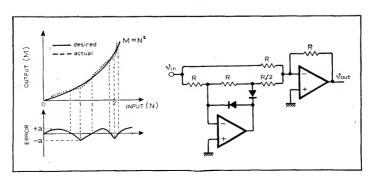

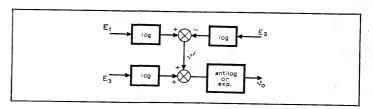

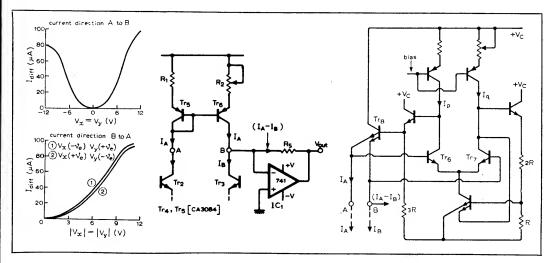

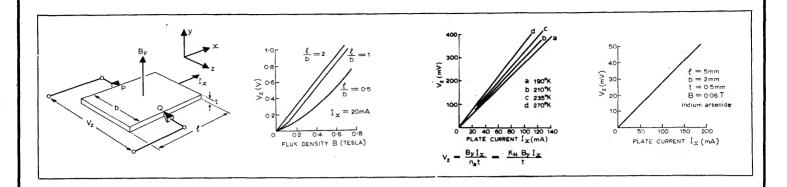

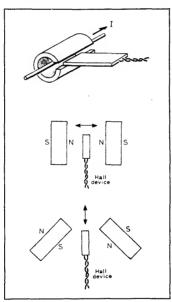

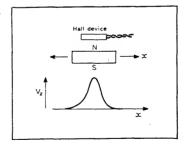

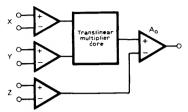

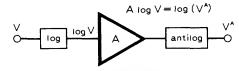

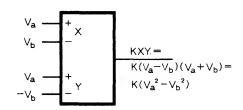

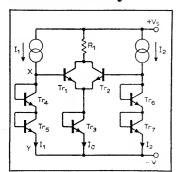

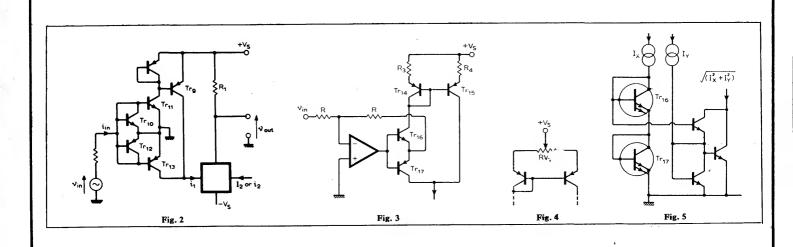

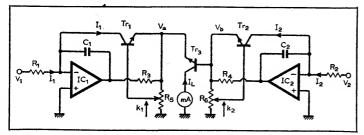

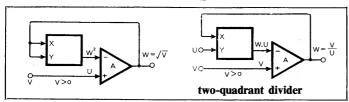

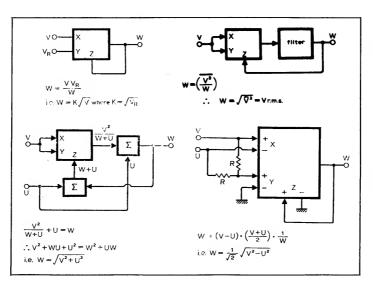

#### Set 29: Analogue multipliers page 115

Background article/quarter-squares multiplier/v-to-f converter multiplier/delta-sigma modulator, multiplier/log-antilog multiplier/triangle-wave averaging multiplier/four-quadrant multiplier—applications/translinear multiplier/multiplier using Hall-effect devices/f.e.t. analogue multiplier/up-date

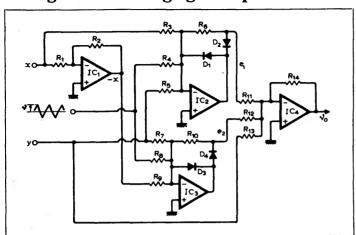

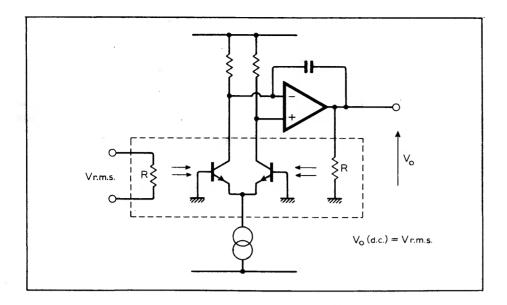

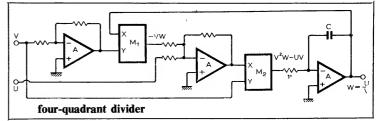

# Set 30: r.m.s./log/power law circuits page 129

Background article introducing non-linear circuits/root-law array/voltage divider/ramp-to-sinewave converter/r.m.s.-to-d.c. converter/D-type delta-sigma converter/cube-law converter/logarithmic amplifier/resolvers/applications of i.c. multipliers/computation of  $(x^2+y^2)^t$ /up-date circuits

# Contents of sets1-20 page 143

# **Preface**

While writing Circards we have often felt like acting out the parts of latter-day Canutes as the tide of innovations sweeps in. There is the feeling that the tide must be halted long enough at least to learn to swim. The biggest worry in electronics can be to pace the learning process so that new knowledge is both absorbed and applied. Too little reading and study, and the designer is continually forced back on a standard repertoire of solutions; too much and there is no time left to apply that knowledge.

The analogy is appropriate in other ways: new developments come in waves, each building on the ones before. A single technical article or new device can set a whole generation of designers off with fresh momentum, each contributing to that tide. In an age when power is assumed to reside only in organizations it is cheering to note how often the origin of such a sequence of waves can be traced to a few individuals. Just as Blumlein in an earlier age provided new and fundamental innovations such as the Blumlein integrator and the long-tailed pair, so in the i.c. age Bob Widlar changed the whole approach to design by such innovations as the current-mirror and band-gap regulators. Some of the most useful and innovative designs in the last couple of years have come from Barrie Gilbert, whose papers are always a source of ideas (if you are going to steal an idea at least steal a good one). The common feature to such designers is their ability to approach problems in a more open way-a state of mind that says "what happens if . . .?"

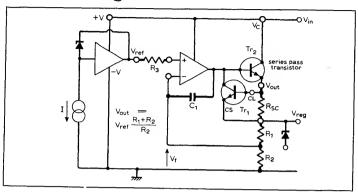

This approach is refreshingly present in much published work in recent years. It would have been all too easy as integrated circuits were produced for particular purposes to close the mind to other alternatives or applications. Fortunately the manufacturers are continually forced to broaden the range of applications of each device. From a production standpoint the i.cs have to be as standardized as possible with the fewest possible connections and simplest processing. A good example is the three-terminal voltage regulator aimed initially at on-card regulation in digital systems. No sooner had it appeared than the applications engineers were set to work to show that it could also be used for variable voltage regulation, as a switching regulator, a current limiter and so on.

It is important for each of us to continue that spirit of controlled curiosity. In Circards we have tried to provide an optimum blend of standard and novel circuits. Clearly with readers having a wide range of interests and expertise we will offend some with out naivety, and baffle others with our obtuseness. Our hope is that the circuits will be useful, but that in addition they will include sufficient new ideas to start a few fresh waves. The nearest tide to sweep in on the analogue shore, that of the functional blocks such as multipliers, V-f and d/a converters, presents a superb opportunity for good design and good designers. To mix the metaphor a little, the alternatives are to sit in the deck-chair or start surfing.

We would like to acknowledge the continuing support and encouragement of the Principal and Governors of Paisley College, the help and advice of colleagues; the excellent judgement of *Wireless World* in supporting this project; and the apparently limitless patience of our wives and families. To these last, this book is dedicated with love.

Peter Williams

#### Set 21: Voltage-to-frequency converters.

You may not find many voltage-to-frequency converter circuits classified as such. They are likely as not to be found under such headings as voltage-controlled oscillators, frequency modulators, astable circuits, and even waveform generators, as the following article—an elementary introduction to their operation—points out. Decisions on which kind to use may often centre on linearity. The closed loop designs generally have better linearity, typically 0.1 to 0.5%, than the simpler openloop designs, especially the "charge dispensing" kind, discussed in the article (see, for example, page 19). The unijunction type, page 10, also crops up on pages 116 & 130, and a further  $\Delta\Sigma$  circuit on page 117.

Background article 8

Unijunction converter 10

Multiplier converter 11

Delta-sigma converter 12

Sinewave converter 13

Multiphase converter 14

Monolithic converters 15

Linearized converter 16

Linear converters 17

Diode-pump converter 18

Differential input converter 19

Up-date circuits 20

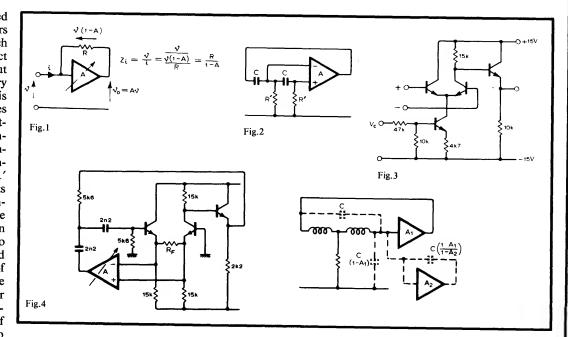

# Voltage-to-frequency converters

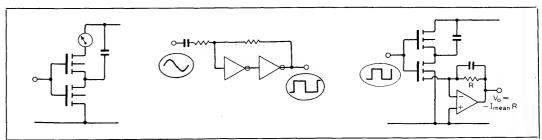

Voltage-controlled oscillators—astable multivibrators—waveform generators—frequency modulators: under each of these headings one finds circuits that have an important common property, that the output frequency is a function of some reference or control signal. Such circuits are multi-variable systems in which several parameters of the output waveform are controlled singly or in various combinations by other parameters at the input. Thus the same circuit can appear under different headings depending on which input/output relationship is of priority concern.

As an example, some recent integrated circuits have been designed as waveform generators with square/triangle/sine wave outputs. If the output waveform is of no particular concern, the fact that the frequency of each output is proportional to a direct control voltage assumes a greater importance. The circuit can then be called a voltage-controlled oscillator. Now assume that the control voltage is set to a particular quiescent value with a smaller alternating voltage superimposed. Then the output frequency is modulated by the a.c. input, with the carrier frequency corresponding to the quiescent value of control voltage. The label for this circuit is frequency modulator.

In set 21 of Circards the primary property of interest is the relationship between an input voltage or current and the frequency of the output, with much less importance being attached to the wave shape or amplitude. A particularly desirable property is that the voltage-to-frequency relationship be linear, and in extreme cases departures from linearity of as little as 0.01% may be desired. In the process of achieving this, the output pulse height and width may have to be equally well controlled but these are a means to the end and not an end in themselves. There are other cases where the frequency needs to be varied only over a limited range, demanding only a small linear region to the V/f characteristic. A good example is found in the design of v.c.os for high-frequency phase-locked loops. Restriction of the frequency range and of linearity is a compromise accepted more or less willingly in exchange for a speed capability that matches that of the associated digital circuits.

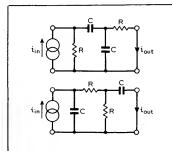

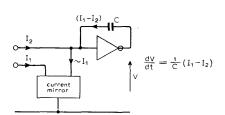

In nearly all of these examples, the basic timing mechanism is that of charging a capacitor from a control voltage or current. The voltage change across the capacitor is sensed by some level-detecting circuit which activates an electronic switch

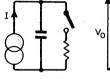

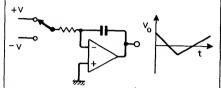

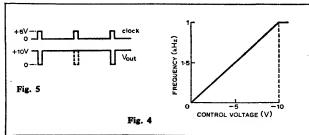

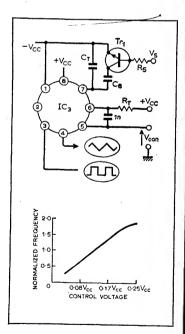

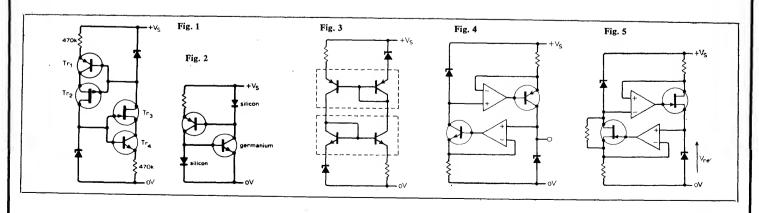

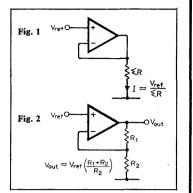

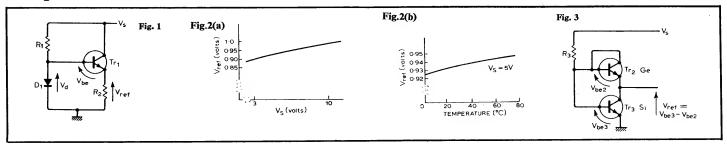

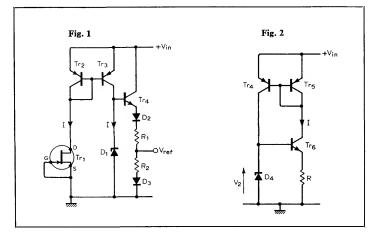

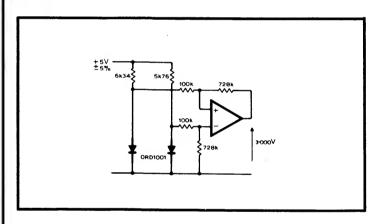

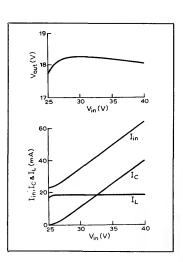

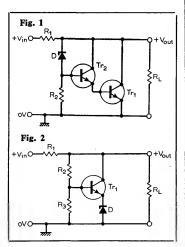

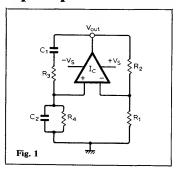

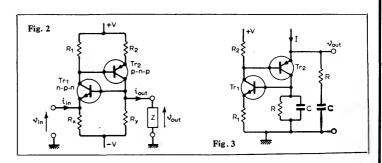

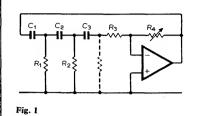

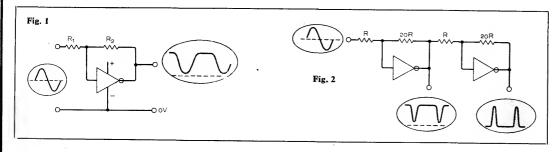

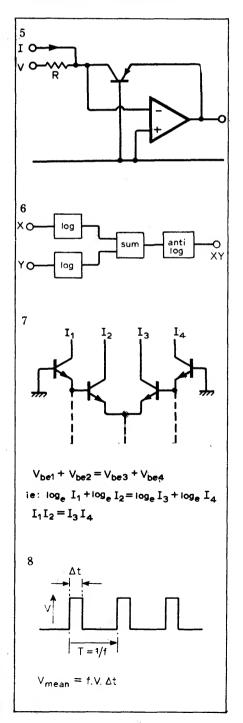

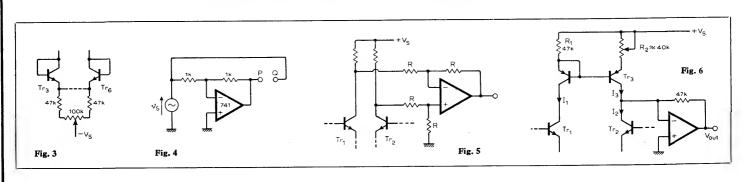

Fig. 1. Constant charging current allows repetition frequency to be made proportional to current.

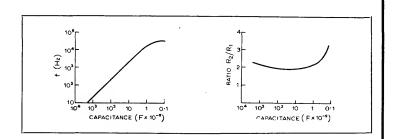

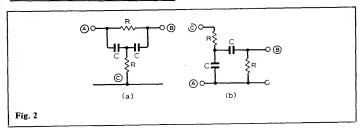

Fig. 2. To cause charging cycle to recommence, a low-value resistor is switched across the capacitor to discharge it quickly.

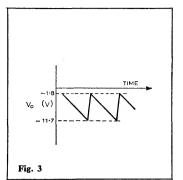

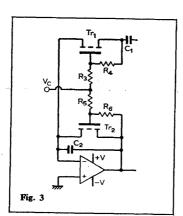

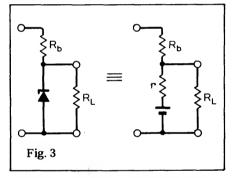

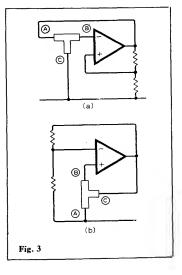

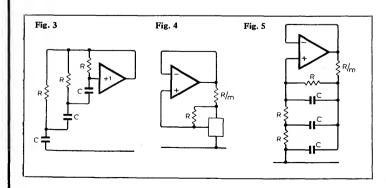

Fig. 3. If discharge time is made small enough the charging current can remain connected. Level of capacitor voltage is used to operate discharge switch.

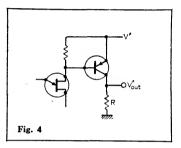

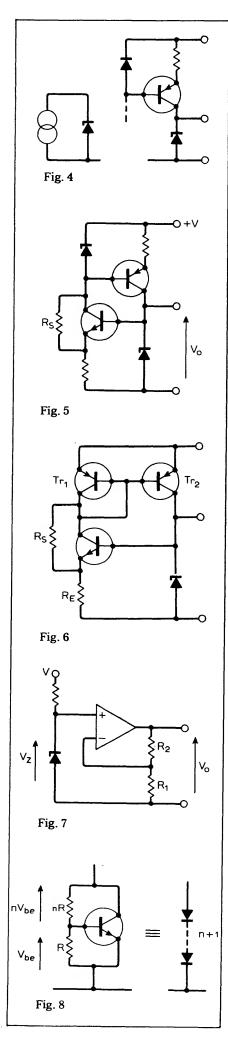

Fig. 4. Triangular waves with repetition frequency proportional to current are produced by reversing capacitor charging current.

to discharge the capacitor and restart the cycle. Two categories of circuit can be clearly distinguished:

• where the discharge time of the capacitor is made short compared with the shortest charging time and need not be under the control of the input voltage, and

• where both charge and discharge times are controlled in common by the input. The first-mentioned circuits produce sawtooth waveforms across the capacitor and short duration output pulses, while the last-mentioned commonly develops a triangular wave across the capacitor, in association with a square wave at a separate output.

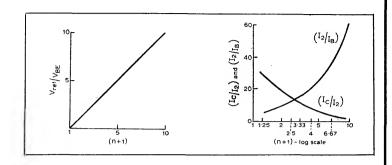

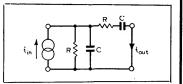

These ideas are illustrated in Figs 1 to 4. In Fig. 1, constant current results in a constant rate-of-change of voltage across the capacitor, i.e. the time taken to charge to a given p.d, will be inverse to the charging current. If that level can be sensed and caused to end the cycle or half-cycle, then the repetition frequency (being inverse to the period of the waveform) will be proportional to the current and a linear I/f converter results. The simplest way of causing the cycle to recommence is to place a lowvalue resistor across the capacitor to discharge it in the shortest possible time. If the discharge current is large compared to the charging current, then it is immaterial whether the charging current is disabled or not and Fig. 3 represents the basic principle of many V/f converters, with the switch periodically closing at the instant when the p.d. across the capacitor reaches a defined value.

An alternative principle is shown in Fig. 4. The current generator is applied to the capacitor in the reverse direction giving an opposing slope to the ramp but of equal magnitude. The resulting waveform is triangular with the repetition frequency linearly related to the current if the points at which switching is initiated are defined. The provision of a purely electronic two-pole change-over switch is difficult, and the reversal of current direction is more often achieved by using a single-pole switch or its equivalent to control the current generator directly.

A second problem that often arises is that the changing p.d. across the capacitor affects the nominally constant current. This is obvious in terms of the non-linearity of the ramp, but may not affect the linearity of the

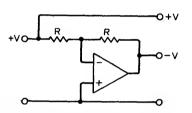

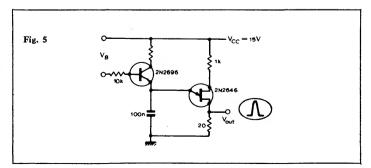

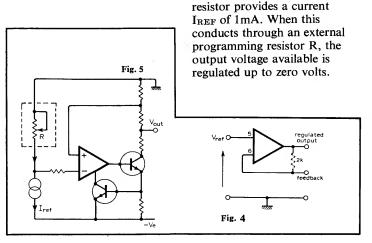

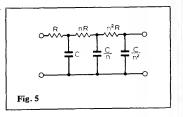

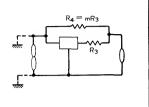

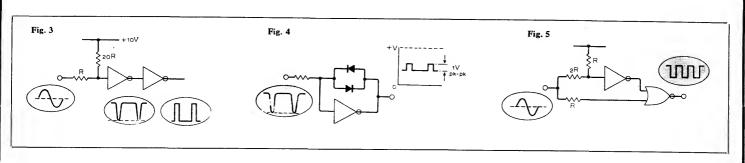

Fig. 5. Using the charging capacitor in an op-amp integrator ensures current is independent of capacitor p.d.

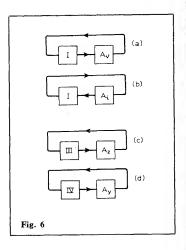

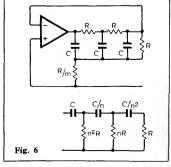

Fig. 6. Simple form of triangularwave generator uses principle of Fig. 5.

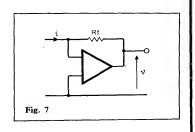

Fig. 7. Circuit provides equal +V and -V inputs for Fig. 6 with an op-amp of -1 gain.

V/f function provided the waveshape is well controlled, e.g. accurate V/f conversion is possible with simple R-C charge and discharge circuits though the wave shape is highly non-linear. Where waveshape is also of importance, the capacitor forms part of an operational amplifier integrator circuit, with the virtual earth action ensuring that the charging current is independent of the p.d. The discharge element now has no point connected to ground which can raise problems in activating it. (Fig. 5.)

This technique leads to a simple form of triangular-wave generator shown in Fig. 6 where both the +V and -V inputs have to vary together if the slopes are to remain of equal magnitude. By using both the input and the output of an amplifier with a voltage gain of -1 this is readily achieved (Fig. 7). Alternative methods include the design of amplifiers whose voltage gain is switched from +1 to -1, and of integrators in which the direction of capacitor current is reversed by a switch while the magnitude is controlled by a single input voltage.

In all of these circuits there remains the problem of the level sensing circuitry that is to determine the instant of switching; both switching speed and accuracy of level are important making the design of a fast, accurate V/f converter a difficult one.

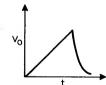

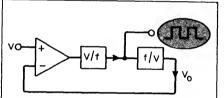

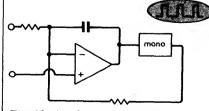

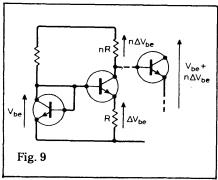

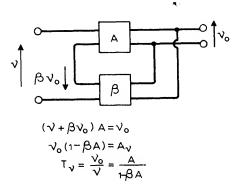

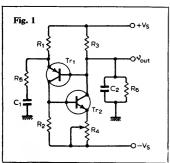

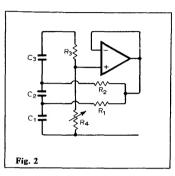

The term charge-dispensing is a big one in the literature on precision V/f converters. A feedback system is set up in which the output pulses from a generator (basically

monostable in form) are arranged to feed back a constant amount of charge for each output pulse. If these units of charge are combined at the input of the system with the control signal, and the overall feedback is negative, then the pulse rate will be proportional to the control signal.

In block-diagram form in Fig. 8, the principle is illustrated by a combination of V/f and an f/V converter. Assuming that the amplifier gain is high, and that the f/V convertor is very linear then the feedback overcomes any non-linearities in the V/f converter, i.e.  $V_o = V$  to a high accuracy because of the feedback while  $V_o \propto f$  ensuring that  $f \propto V$  without reference to the linearity of the V/f converter. The f/V converter might be of the diode-pump variety which with suitable design can transfer a fixed charge into a load for each output pulse rate.

A level-sensing monostable gives an output pulse when the input level rises above a critical value. If the input then falls a second pulse is generated on the next excursion through the set level in the same sense. An important restriction is that the capacitor shall have been completely discharged prior to the second pulse—otherwise the time taken for recharging will be shortened and the output pulse-width reduced. The output of such a monostable would ideally be a train of constant-amplitude constant-width pulses, which could be smoothed and fed back to the input amplifier as in Fig. 9.

Fig. 8. In this "charge-dispersing" system, a constant amount of charge for each output pulse is fed back so that pulse rate can be proportional to the control signal.

Fig. 9. Monostable circuit produces output pulse when input exceeds a certain level, in either sense.

Fig. 10. An alternative arrangement is to dispense charge into a summing integrator. Output pulse rate is a linear function of control voltage or current.

Fig. 11. Technique of using two current sources, but switching only the one having twice the value of the other, is used in some i.cs.

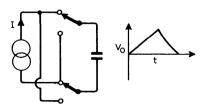

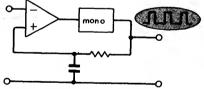

Fig. 12. Triangular wave generator using technique of Fig. 11.

Comparator reference inputs are set to 2V/3 and V/3, the capacitor voltage ranging between these limits.

A better arrangement dispenses these units of charge into a summing integrator—Fig. 10. For positive pulses a negative control voltage is required, the integrator output ramping up until a pulse is produced from the monostable. The charge dispensed into the summing junction causes the output of the integrator to fall, again rising slowly under the action of the control current. On average, the net charge inflow has to be zero, the charge dispensed per pulse is constant and hence the pulse-rate is a linear function of the control voltage/current.

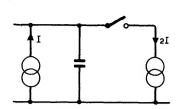

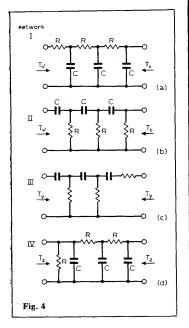

Other recent i.cs revert to the separate constant current circuit for timing circuits and waveform generators, and the resulting I/f linearity can be accurate enough for many applications. One technique is to have two current sources one set by the external control voltage, the other of opposite polarity but of twice the magnitude—Fig. 11. Keeping the former permanently on and switching the latter on and off makes the net current in the capacitor change from +I to -I. A circuit configuration to use this technique to produce a triangular-wave generator is shown in Fig. 12.

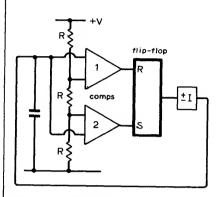

Two comparators sense the capacitor voltage, their reference inputs being set to +V/3 and +2V/3 by an internal potential divider. Assume the current at I; the capacitor charges until its p.d. reaches +2V/3. Comparator 1 changes its output and resets the flip-flop. This reverses the direction of current flow until the capacitor discharges to +V/3. The comparator 2 operates setting the flip-flop into its original state and restarting the cycle.

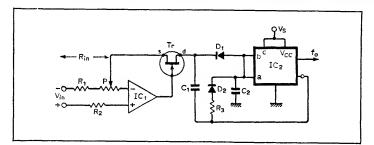

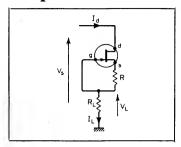

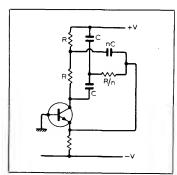

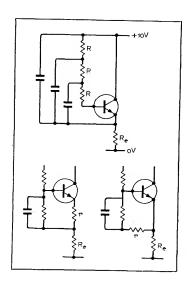

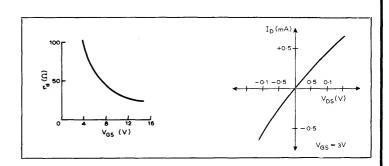

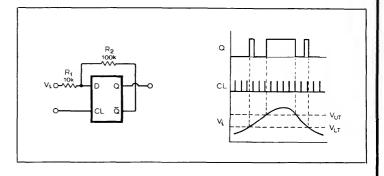

#### Unijunction voltage-to-frequency converter

#### Components

IC 741,  $\pm 15V$  supplies

Tr 2N2646

C 10nF

R 100kΩ

V′ 3.3V

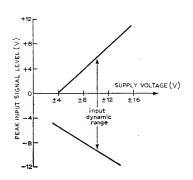

Vin see graph

Vo see graph

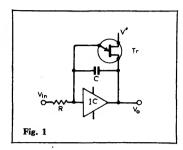

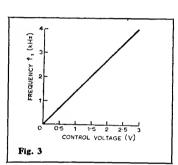

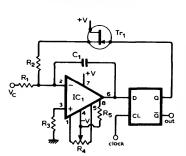

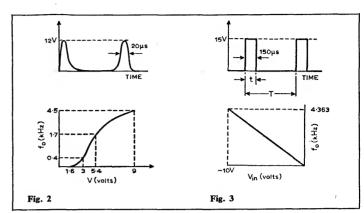

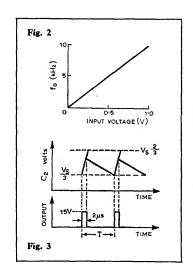

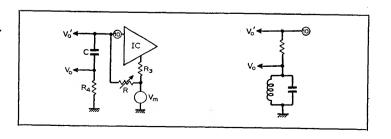

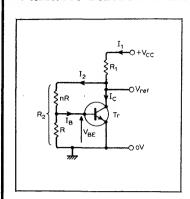

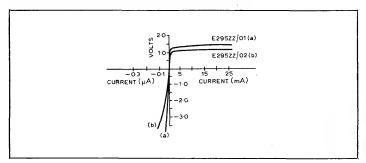

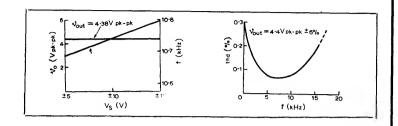

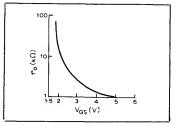

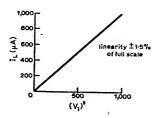

Circuit description With the removal of the unijunction transistor the circuit of Fig. 1 is simply an integrator which, with a positive V<sub>in</sub>, gives a negative-going ramp V<sub>0</sub>. If the i.c. gain is sufficiently high then  $V_0$  is  $-V_{in}t/RC$ . The unijunction serves to discharge the capacitor each time the voltage between e and b. reaches the unijunction trigger voltage. The circuit therefore goes through the cycle shown right. Upper limit of -1.8V is the voltage at which the unijunction reverts to being an open circuit. Lower limit of -11.7V is arbitrary and is the result of choosing V', R and C so that  $V_{in}=10V$  gave a frequency of 1kHz. With ±15V supplies this obviously cannot be extended beyond 15V. The degree of linearity in the plot of frequency against Vin shown in Fig. 2 is quite high e.g. 10V gave 1kHz, 5V gave 498Hz, 1V gave 96Hz and 0.15V gave 16Hz. Rise time of the output waveform (Fig. 1 circuit gave the waveform of Fig. 3) corresponding to the time when C is discharging, was  $15\mu$ s i.e. 1.5% of the period at 1kHz, so the circuit cannot be recommended for much higher frequencies.

But from the expression for the downward ramp it is clear that the same frequency range can be achieved by the use of different values of R and C, and also of V'. It will, of course, be generally desirable to keep R relatively high to give high input impedance.

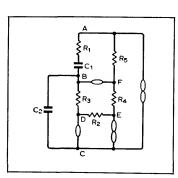

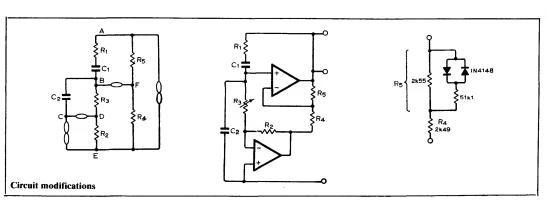

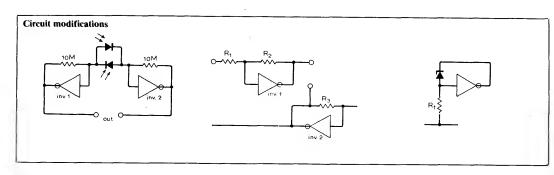

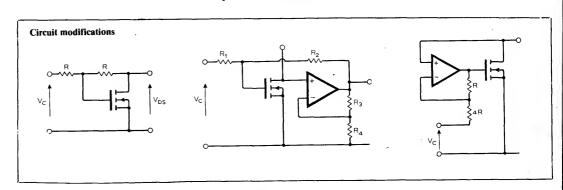

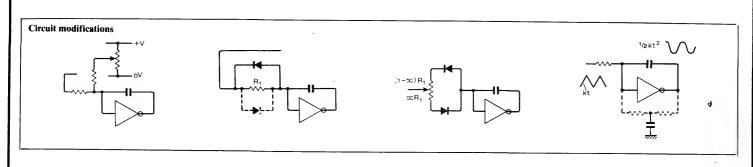

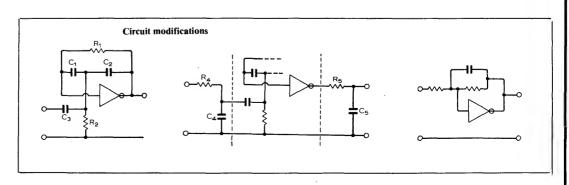

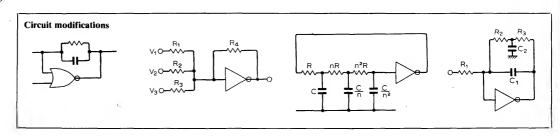

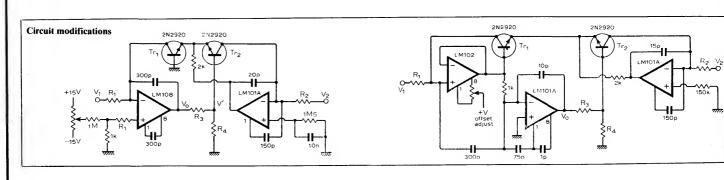

#### Circuit modifications

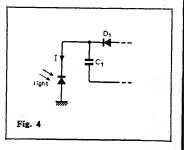

The modification shown in Fig. 4 to the circuitry around the unijunction transistor will provide a pulse train at  $V_0$ , the frequency being the same as that of the main circuit. The leading edge of this pulse train will correspond to the rising edge of  $V_0$  shown in Fig. 3. This  $V_0$  will, of course, have the advantage of going much closer to zero in the time between the pulses.

An alternative voltage-to-frequency converter reported by Swarup and Banerjee is shown in Fig. 5. It is basically a unijunction oscillator with constant-current drive to the capacitor, this

current being proportional to the voltage  $V_{\rm B}$ . A linear relationship between  $V_{\rm B}$  and the output frequency is claimed in the range 0 to 500Hz. The basic action of the unijunction oscillator and modifications to reduce the discharge time of C are fully described in Circards set 3 (waveform generators) card 4.

#### Reference

Swarup & Banerjee, Linear voltage to frequency and voltage to pulse width converters using unijunction transistors. *Int. J. Electronics*, vol. 32, 1972, pp. 377-81.

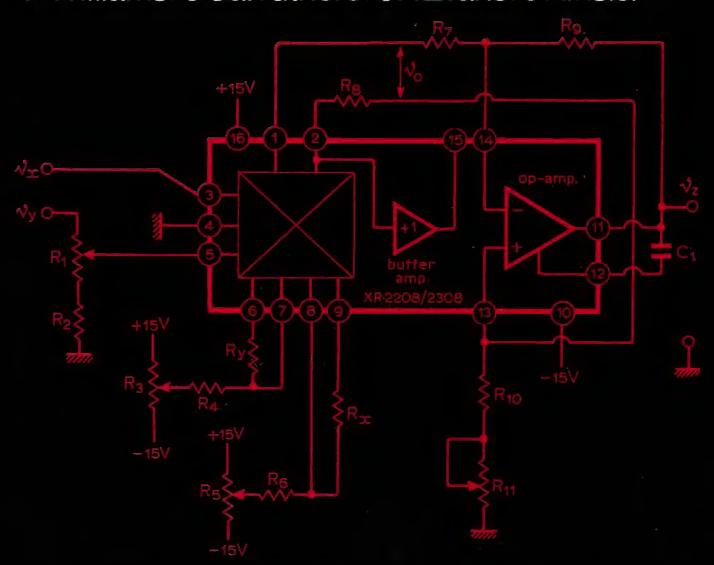

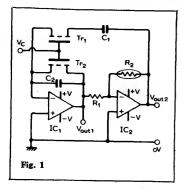

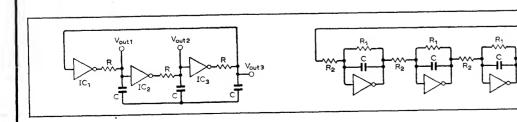

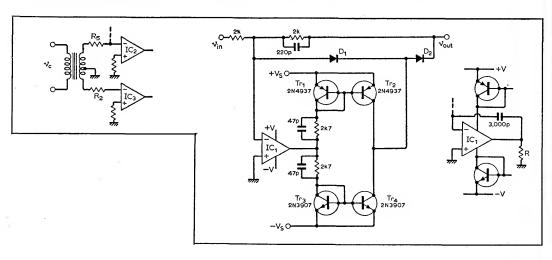

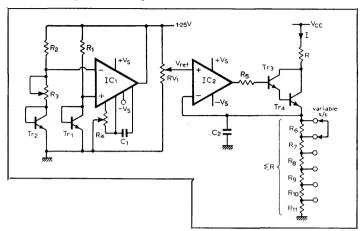

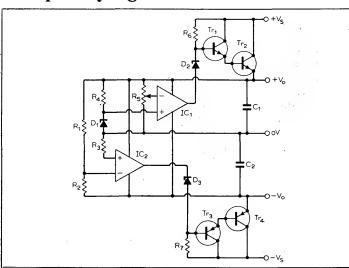

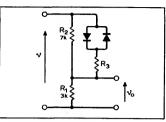

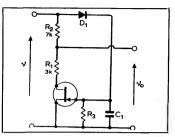

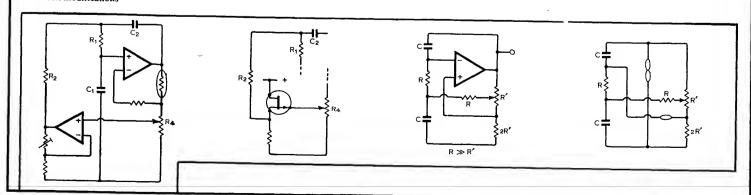

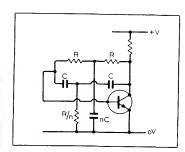

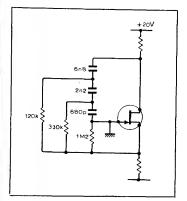

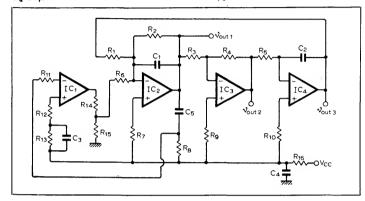

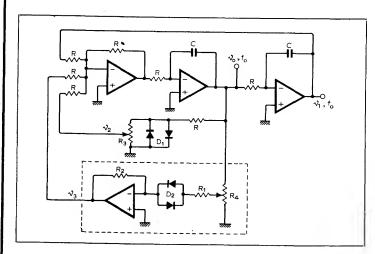

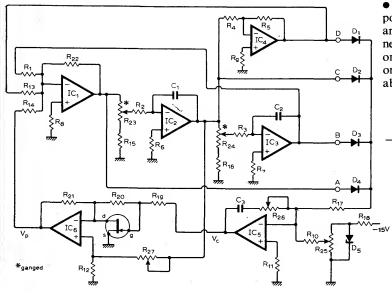

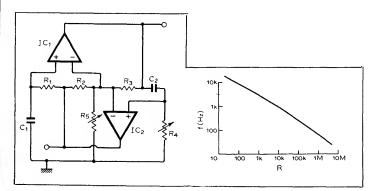

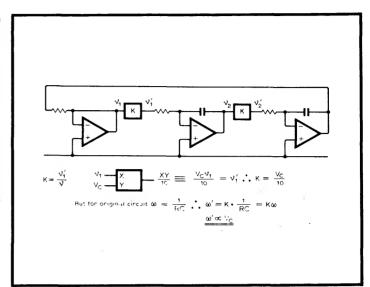

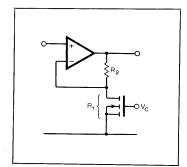

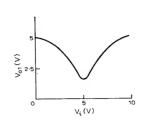

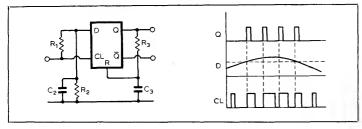

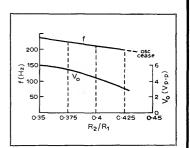

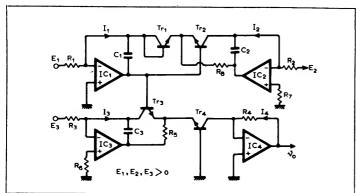

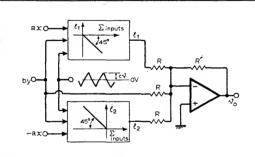

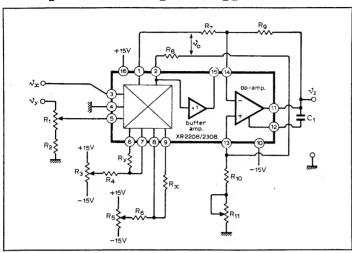

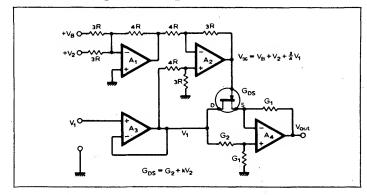

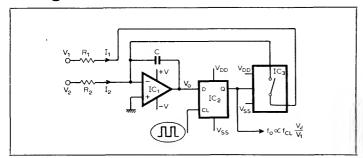

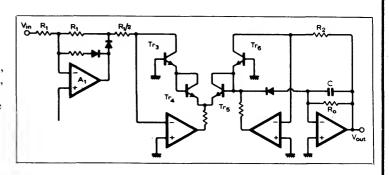

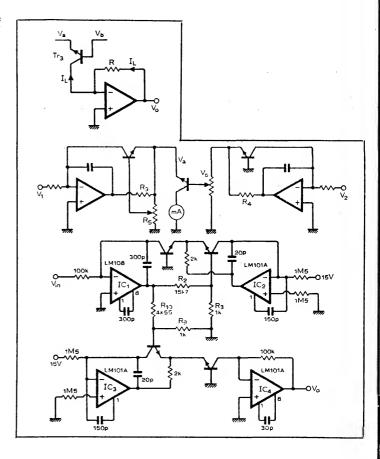

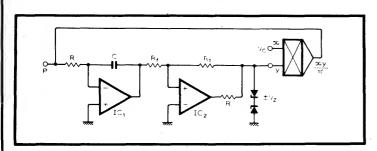

#### Multiplier voltage-to-frequency converter

Circuit description

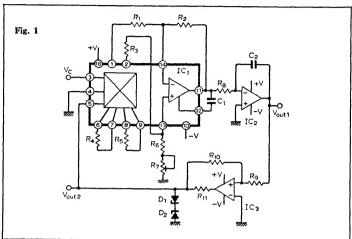

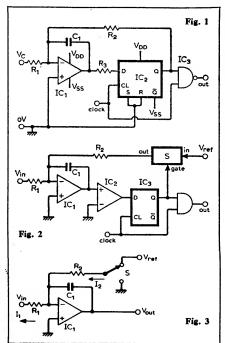

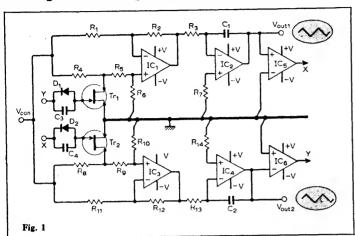

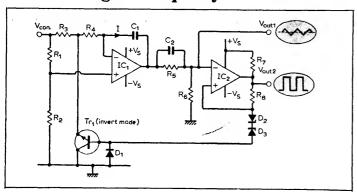

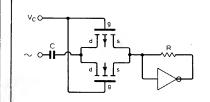

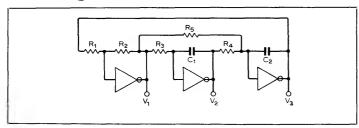

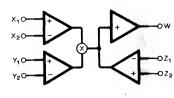

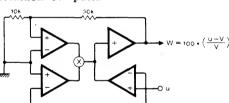

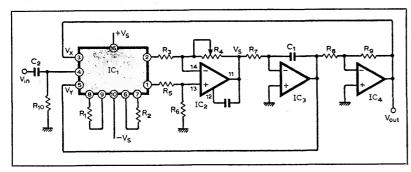

The circuit of Fig. 1 is basically a closed-loop integrator-comparator square-triangle generator, comprising IC<sub>2</sub> and IC<sub>3</sub>, with a multiplier (IC<sub>1</sub>) inserted in the loop to provide control of frequency. The value of the output voltage from the multiplier is a scaled version of the product Vout2 and the control voltage V<sub>C</sub>. Thus the amplitude of the signal to be integrated is directly proportional to a scaled value of the control voltage. A positive voltage applied to the inverting integrator charges C2 with its output end negative relative to the input end (held close to 0V by negative feedback through C2 and the high gain of IC2). Thus, Vout1 goes negative until the current it feeds through R, exceeds the positive current in R<sub>10</sub>, resulting in a negative current to the non-inverting input of the Schmitt comparator. Vout2 then rapidly switches to a negative value due to positive feedback applied to IC<sub>3</sub>, causing the multiplier output to go negative (Ve is always positive). The output from the integrator then starts rising until it reaches a positive voltage sufficient to make the comparator change its state again, returning Vout2 and the multiplier output to their original positive values. Hence, Vout1 is a triangular

wave and Vout2 a square wave with frequency linearly dependent on the control voltage

Component changes

Useful range of supplies: ±7 to  $\pm 16V$ .

Increase C<sub>2</sub> to reduce upper frequency limit.

Useful range of Ve is about 0 to +11 V.

Changing IC<sub>3</sub> to a 301 type op-amp increases slew-rate capability.

R<sub>9</sub> can have a wide range of values the lower limit being imposed by heavy loading of IC<sub>2</sub> and the upper limit by the failure of IC<sub>3</sub> to switch before it saturates.

#### Circuit modifications

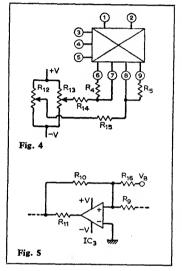

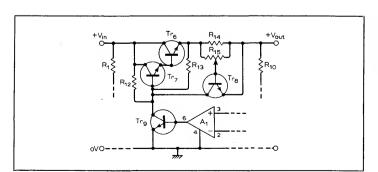

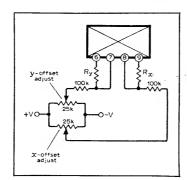

- Accuracy of frequency control largely depends on the nonlinearity and offset voltages in the multiplier part of the loop. Output offset adjustment is provided by R7 and independent adjustment of the offset voltages at the multiplier's X and Y inputs (pins 3 and 5) can be obtained by the 25-k $\Omega$  potentiometers R<sub>12</sub>, R<sub>13</sub> shown in Fig. 4, where  $R_{14}$ ,  $R_{15}$  are  $100k\Omega$ .

- For a given value of control voltage frequency depends on the scale factor of the multiplier. Adjusting this allows the output frequency to be made a simple linear function

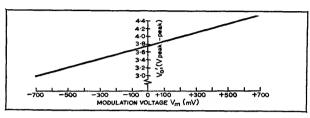

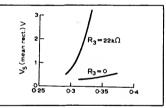

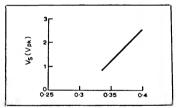

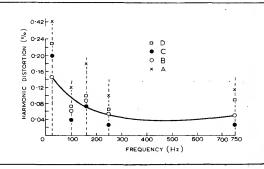

Typical performance

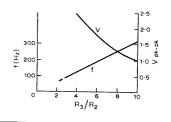

Supplies  $\pm 15V$ ,  $\pm 8.5mA$ IC<sub>1</sub> XR2308 IC<sub>2</sub>, IC<sub>3</sub> 741  $D_1$ ,  $D_2$  3.3V Zeners  $R_1$ ,  $R_3$  22k $\Omega$  $R_2$ ,  $R_6$  330k $\Omega$   $R_4$ ,  $R_5$  68k $\Omega$   $R_7$  100k $\Omega$   $R_8$ ,  $R_9$ ,  $R_{10}$  10k $\Omega$  $R_{11}$  2.2k $\Omega$   $C_1$  22pF,  $C_2$  1nF See Fig. 3 for graph of f/Ve and Fig. 2 for waveforms.

- of Ve. The factor can be adjusted in three ways: (1) by adjusting the op-amp gain in the multiplier block by means of R<sub>2</sub>, (2) by adjusting the gain of the multiplier block by varying R<sub>4</sub> and R<sub>5</sub>, and (3) by connecting the  $V_{\mathrm{out_2}}$  signal to the Y input of the multiplier (pin 5) through a ground-referred potentiometer.

- Asymmetry in the output waveforms due to mismatched Zener diodes can be corrected by applying a bias voltage  $V_{\rm B}$ of suitable polarity to the comparator input via R<sub>16</sub>, as shown in Fig. 5. Alternatively, this arrangement with  $V_{\rm B} = \pm V$ and  $R_{16} = 10k\Omega$  can be used to purposely introduce a d.c. offset into the output waveforms.

- Other methods may be used to limit the amplitude of the output voltage from the comparator, e.g. by using a diode bridge limiter or by replacing IC<sub>3</sub> with an op-amp of the type providing access to the drive point of its output stage, such as a 748. This allows the comparator output to be

clamped by zener diodes or suitably-biased transistors connected to the output stage drive point.

• For higher frequency operation the multiplier/op-amp block can be replaced by a separate multiplier (MC1495) and inverting amplifier (LM318), the 741-type integrator replaced by an LM318 integrator and the Schmitt replaced by an LM311.

Further reading

Graeme, J. G. Applications of operational amplifiers. McGraw-Hill 1973, pp. 161/2. Graeme, J. G., Tobey, G. E. & Heulsman, L. P. Operational amplifiers, McGraw-Hill 1971, pp. 237-51. XR-2208/2308 operational multiplier data sheet, EXAR

Integrated Systems Inc. 1972.

Cross references

Set 2, card 1 Set 3, cards 1, 5 Set 13, card 9 Set 17, cards 3, 6 Set 21, card 4

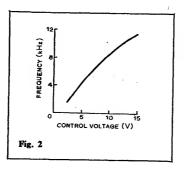

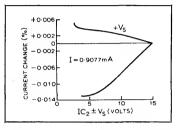

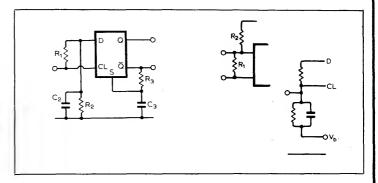

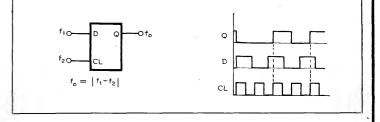

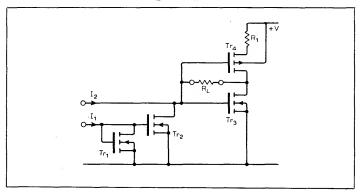

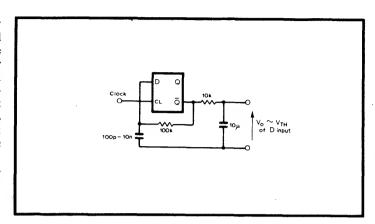

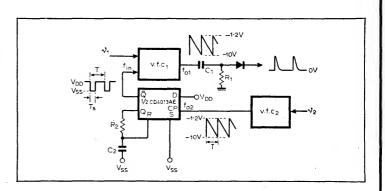

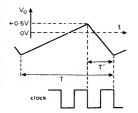

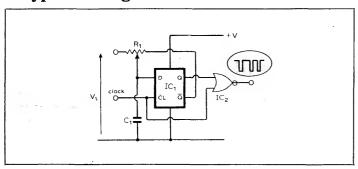

#### Delta-sigma voltage-to-frequency converter

Typical performance of Fig. 1 IC<sub>1</sub> 741, IC<sub>2</sub> 1×CD4013AE IC<sub>3</sub> ½×CD4011AE Supplies  $V_{\rm DD}$  +10V  $V_{SS}$ -10V  $R_1$ ,  $R_2$  100k $\Omega$  $R_2 1k\Omega$ C<sub>1</sub> 100nF Clock 6V positive pulses, p.r.f. 1kHz, duty cycle 10% See Figs 4 and 5.

Circuit description

A class of voltage-to-frequency converter gives an output in the form of a pulse train where the repetition frequency is directly proportional to the instantaneous value of the control voltage but the pulses are generated asynchronously. The output from a delta-sigma encoder is again a pulse train but its average pulse repetition frequency is proportional to the control voltage and the pulses are generated in synchronism with a clock pulse waveform. The basic form of a delta-sigma modulator is essentially a voltage-to-pulse ratio converter (Fig. 3). The circuit maintains a constant voltage across C1 as the input voltage is varied. which requires that the charging current from the voltage reference source to be switched into C<sub>1</sub> at a repetition rate that attempts to keep the net change in voltage across C1 at zero. Thus the rate at which the reference current must be switched into the capacitor must be proportional to the input voltage. If the reference current is switched under the control of a stable clock-pulse

generator the output pulses will be proportional to  $V_{in}$  and synchronized with the clock pulse source. Assuming that the net voltage across  $C_1$  is zero, that  $V_{in}$  is negative, that  $V_{ref}$  is positive and  $IC_1$  is a high-gain op-amp then  $I_1=I_2$ ,  $V_{out}$  (mean) =0 and  $I_{out}$  (mean) =0. As the inverting input of  $IC_1$  is a virtual earth,  $I_1=V_{1n}/R_1$  and  $I_2=kV_{ref}/R_2$  where k is pulse duty cycle required to keep  $I_2=I_1$ . Equating these currents gives

$$\frac{V_{\rm in}}{R_{\rm i}} = k \frac{V_{\rm ref}}{R_{\rm 2}},$$

where k is the ratio of the output pulse repetition rate (f) to the clock pulse repetition rate (f<sub>c</sub>). Hence

$$f = \left(\frac{R_2 f_c}{R_1 V_{ref}}\right) V_{in}.$$

By making  $R_2 = R_1$  and  $V_{\text{in}(\text{max})} = V_{\text{ref}}$  the maximum output p.r.f. is that of the clock source and the average output pulse rate is proportionally smaller for smaller values of  $V_{\text{in}}$ . The arrangement of Fig. 2 uses an analogue transmission gate to realize the switch S.

IC<sub>2</sub> is a precision comparator which determines when the reference voltage source is to be switched to R<sub>2</sub> by monitoring the polarity of the output from the integrator IC<sub>1</sub>. This switching action is synchronized to the clock pulses by using gating pulses derived from the output of a D-type flip-flop which receives the comparator's output at its data input. The circuit of Fig. 1 is that to which the typical performance data refers. This is a simplified form of the arrangement previously discussed with the electronic switch, separate reference source and precision comparator removed. (Note that whilst the integrator used both positive and negative

Fig. 6

supplies the D-type flip-flop is connected only across the positive supply.) As the D-type produces output pulses equal in amplitude to the  $V_{\rm DD}$  rail voltage only when its data input receives a positive pulse from the integrator, a separate switched reference is not essential. Also, the precision comparator can be replaced by R<sub>a</sub> which limits the negativegoing pulses to the data input of the D-type which acts as the comparator. Average frequency/Ve graph (Fig. 4) has a linearity of  $\pm 0.1\%$  up to  $f=f_c$  when  $V_c=V_{DD}$ . No further increase in frequency is possible except by increasing the p.r.f. of the clock source. Output pulse waveform of Fig. 5, inverted by IC<sub>3</sub>, is of  $V_{\rm c} = V_{\rm DD}/2$ , the dashed pulse only being present when Ve is raised to V<sub>DD</sub>. The circuit of Fig. 6 is another simplified form of the more general system where the comparator had been omitted and the electronic switch is realized by a junction f.e.t. The positive supply rail is used as the voltage reference source and the output is taken from the Q terminal of the D-type flip-flop IC2, which is a complementary m.o.s. version to conserve power. This circuit is capable of linear v-to-f conversion within  $\pm 0.05\%$ almost independently of temperature changes. Typical values are: V ±2.7V IC<sub>1</sub> LM4250C IC<sub>2</sub> ½×MC14013CL  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$  100k $\Omega$

Further reading

Tr<sub>1</sub> 2N4396

$R_5$  5.6M $\Omega$ ,  $C_1$  100nF

Defreitas, R.Low-cost way to send digital data, *Electronics Design*, pp. 68-73, Jan. 18. 1974 Ross, P. J. Simple accurate voltage to frequency converter. *Jnl. of Physics E*, vol. 7, pp. 706/7. Alusten, B. Calculate with a v-f converter, *Electronics Design*, June 7, 1974, pp. 130-2.

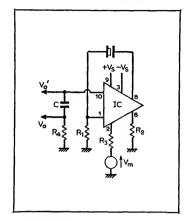

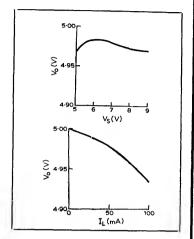

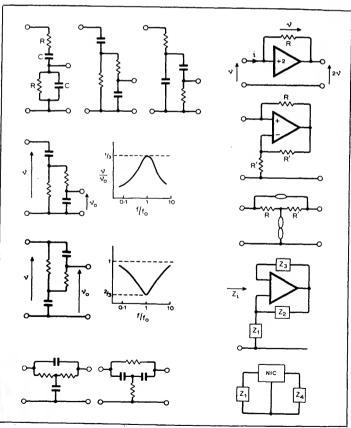

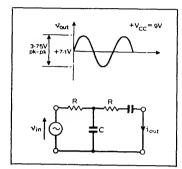

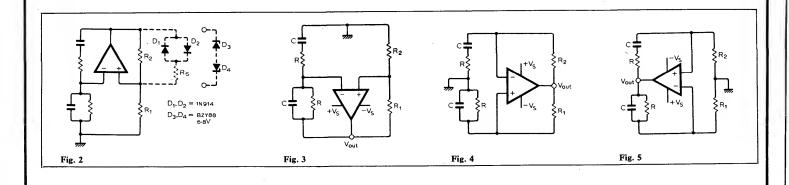

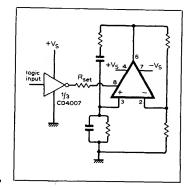

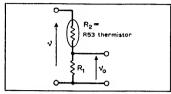

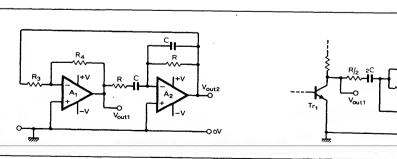

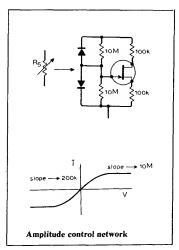

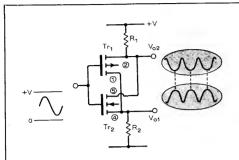

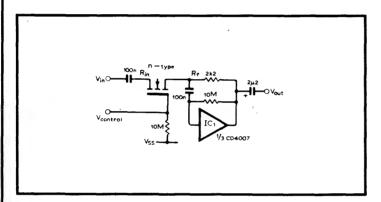

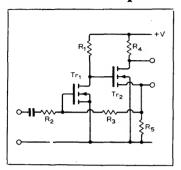

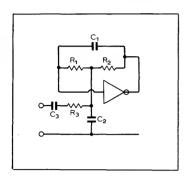

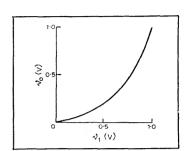

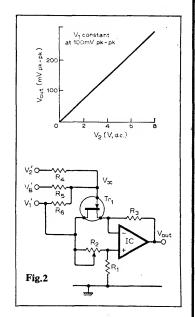

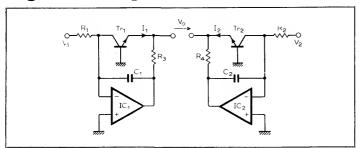

# Sinewave voltage-to-frequency converters

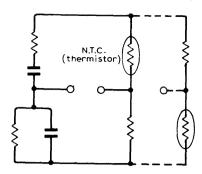

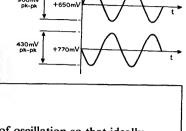

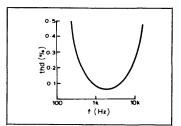

Typical performance Supplies  $\pm 15V$ IC<sub>1</sub>, IC<sub>2</sub> 741 Tr<sub>1</sub>, Tr<sub>2</sub>  $1/6 \times \text{CD4007AE}$ R<sub>1</sub>  $150\Omega$ R<sub>2</sub> thermistor type R13 C<sub>1</sub>, C<sub>2</sub> 100nF  $V_{\text{out}_1}$  520mV pk-pk  $V_{\text{out}_2}$  1.04V pk-pk See graph for f/V<sub>c</sub> (Fig. 2)

Circuit description

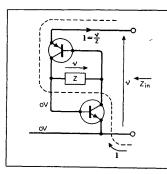

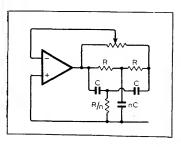

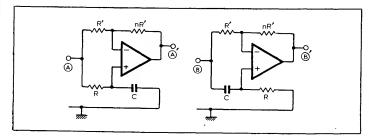

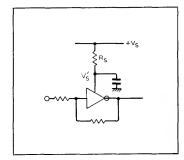

This circuit (Fig. 1) is one of the many forms of Wien bridge oscillators with Tr<sub>1</sub> and C<sub>1</sub> forming the series-connected frequency-dependent arm with Tr<sub>2</sub> and C<sub>2</sub> forming the parallel connected arm of the bridge. For oscillation to occur the closed-loop gain must be unity, the required amount of gain being provided by the inverting operational amplifier IC2, the gain being determined by the ratio  $R_2/R_1$ . With this configuration the commonpoints of the frequencydetermining resistors are connected to the virtual-earth inverting input of IC1. This is a convenient arrangement for replacing these resistors with elements which have a resistance that can be controlled by a ground-referred voltage source. In the above circuit these elements take the form of a pair of matched c.m.o.s. transistors which have gatesource resistances that depend

on the control voltage Ve. Linearity of the voltage-tofrequency conversion characteristic is not particularly good over a wide range of frequencies but may be adequate for many purposes where only a restricted frequency range is required. Resistance of the f.e.ts depends on their drain-source signal voltages as well as on the control voltage Vc but this can be reduced, and the linearity of f.e.t. resistance-to-control voltage characteristic linearized. by using local feedback around the f.e.ts as shown in Fig. 3, where R<sub>3</sub>, R<sub>4</sub>, R<sub>5</sub> and R<sub>6</sub> may be of the order of  $1M\Omega$ . If the closed-loop gain deviates from unity the amplitude of oscillation will vary with time, so to avoid extremely precise setting of gain it is initially set slightly high and then automatically controlled the a.g.c. being achieved with a thermistor in the above circuit. In addition to the use of local feedback on the f.e.ts, these elements could be connected to form only part of the frequency-determining resistances with bulk of the values in the form of seriesconnected resistors which would tend to swamp out the non-linearities in the f.e.t. whilst restricting the range of control. The f.e.ts could be replaced by matched photoconductive resistors or by bipolar transistors which are switched on and off by current pulses to the bases, the mean collectoremitter resistance being controlled by the pulse

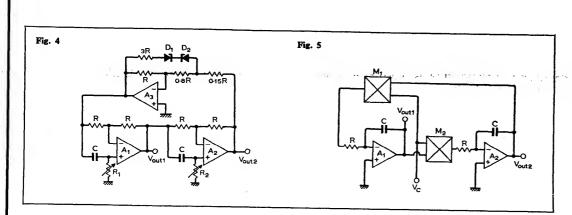

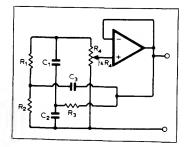

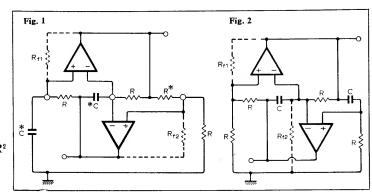

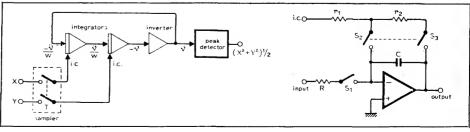

repetition frequency. A voltage-to-frequency converter using a pair of all-pass active networks is shown in Fig. 4. These networks, using A<sub>1</sub> and A<sub>2</sub>, have a constant gain magnitude but a phase shift given by  $\phi_1 = -2\tan^{-1}(\omega CR_1) - 180^{\circ}$  and  $\phi_2 = -2 \tan^{-1}(\omega C R_2) - 180^\circ$ respectively. With the 180° phase shift through the a.g.c. amplifier A<sub>3</sub> the circuit will oscillate at a frequency  $1/(2\pi C\sqrt{R_1R_2})$ Hz, which shows that a voltage-to-frequency conversion may be obtained by making R<sub>1</sub> or R<sub>2</sub> or both voltage-dependent resistors, e.g. f.e.ts. For a wide range of frequency variations R<sub>1</sub> could be a voltage-dependent resistor and R<sub>2</sub> a range-switching resistor. For  $R = R_1 = R_2$  the outputs are generated with a controllable phase difference  $\phi = (\phi_1 - \phi_2) = -2\tan^1(\omega CR).$ Circuit of Fig. 5 uses two active integrators and two multipliers to produce a voltage-tofrequency converter having quadrature outputs that can have a very fast response to changes in V<sub>c</sub> provided a fast a.g.c. system is added to the basic circuit. Under this condition the circuit will oscillate at a frequency which allows the double integration to take place without changing the amplitude of the signal. Multiplier M2 provides an output  $V_2 = + V_c \cdot V_{out_1}/10$  and M<sub>1</sub> gives an inverted output, to maintain the loop phase shift, of  $V_1 = -V_c$ .  $V_{out_2}/10$ . With the 1/10 scaling factor, frequency of oscillation is  $V_c/20\pi RC$ . Multiplier M<sub>1</sub> could be replaced by an inverting operational amplifier.

Further reading Von Ow, H. P., Reducing distortion in controlled attenuators using FETS. Proc. IEEE, 1968, pp. 1718/9.

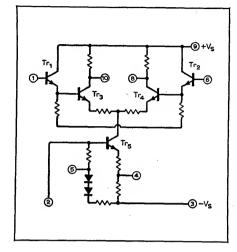

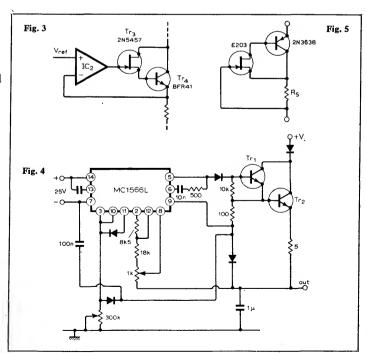

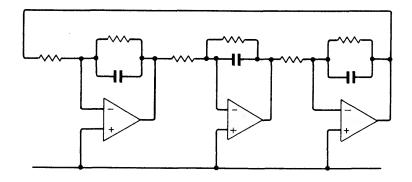

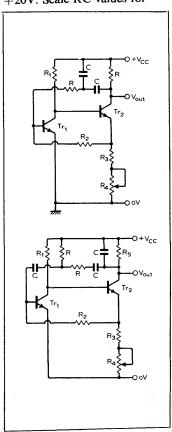

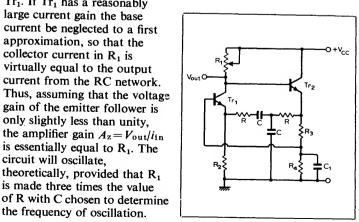

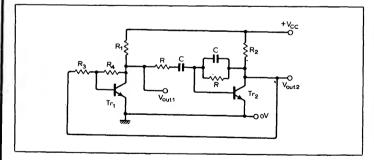

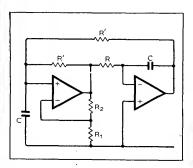

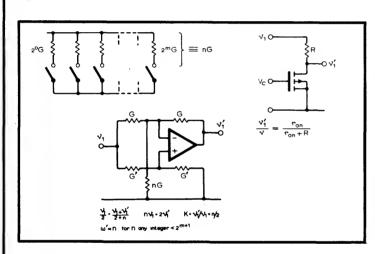

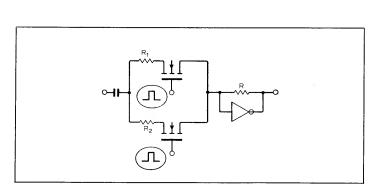

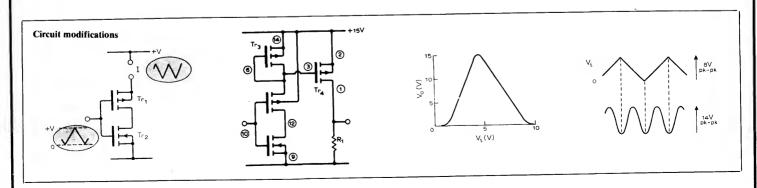

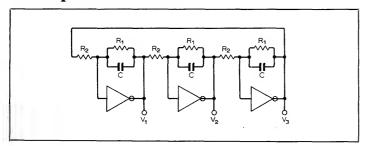

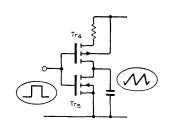

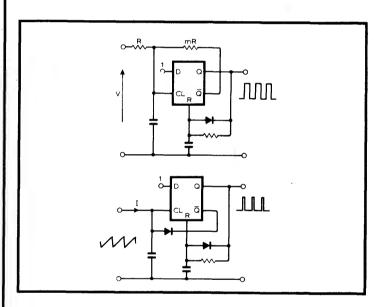

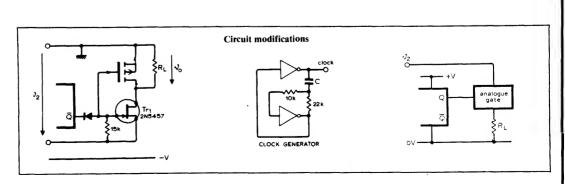

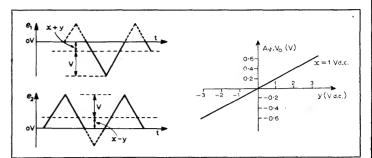

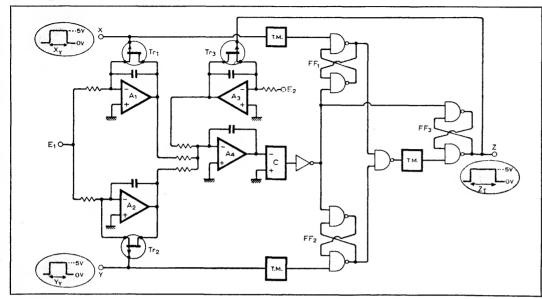

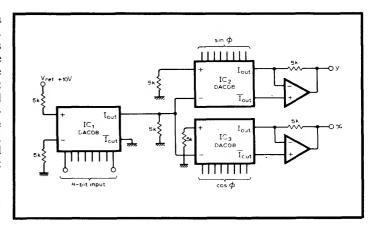

#### Multiphase voltage-to-frequency converter

Circuit description

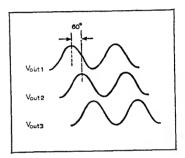

This is a twin circuit based on R-C integration to provide the triangular waveform and level sensing to provide a square wave which operates an electronic switch controlling polarity applied to the integrator. Outputs X and Y are cross-connected giving control of electronic switches Tr<sub>2</sub> and Tr<sub>1</sub> respectively and triangular waveforms which are 90° out of phase. IC5 and ICs provide high open-loop gain, and at low frequencies provide faster switching than comparators. Vout, is a positive-going ramp until Tr. changes state and this occurs at the instant of zero-crossing of Vout2, which then switches IC<sub>6</sub>. Vout1 then ramps down and changes the state of Tr<sub>2</sub> when a zero-crossing point is reached. The time taken to go from say a positive peak to zero level depends on the RC time constant and the value of V<sub>control</sub>. It should be noted that as no amplitude controls for the output are imposed, one or other of the integrators

will reach saturation before the other output reaches its zero crossing point.

#### Circuit modifications

• Use a switched integrator rather than a switched gain amplifier. This makes IC<sub>1</sub>, IC<sub>3</sub> redundant (Circard Set 3, No. 5). LM3900 quad package may be now arranged to provide the two outputs.

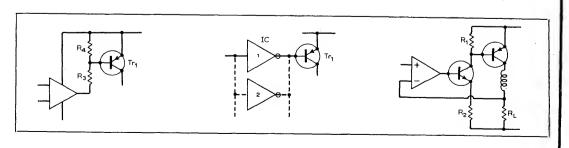

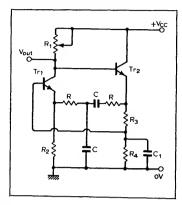

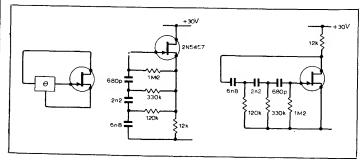

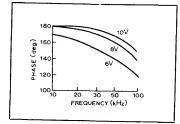

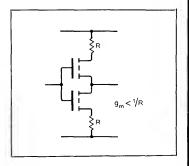

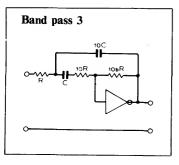

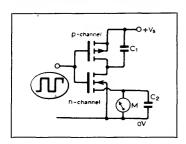

Phase shift oscillator (above) provides three outputs with 60° phase relationship.  $IC_1-IC_3$ : 1/6×CD4049, R:  $10k\Omega$ , C: 2700pF, frequency: 13kHz. As the c.m.o.s. gates are being used in their linear region, both the n- and p-type transistors will be conducting and hence power consumption will depend on the supply voltage. Typically the total current drain from the supply for the above network is  $V_{DD} - V_{SS} = 3V$   $V_{DD} - V_{SS} = 10V$   $V_{DD} - V_{SS} = 15V$  $I_{\rm T}=0$  $I_T=12mA$  $I_{\rm T}=30{\rm mA}$ Frequency may be controlled by substituting voltage-

dependent resistors for each R<sub>1</sub>

Typical data IC<sub>1</sub> to IC<sub>6</sub> 74IC Tr<sub>1</sub>, Tr<sub>2</sub> 2N5457 R<sub>1</sub>, R<sub>11</sub> 20k $\Omega$  R<sub>2</sub>, R<sub>3</sub>, R<sub>12</sub>, R<sub>13</sub>, R<sub>6</sub>, R<sub>7</sub>, R<sub>10</sub>, R<sub>14</sub> 10k $\Omega$  R<sub>4</sub>, R<sub>5</sub>, R<sub>8</sub>, R<sub>9</sub> 2.7k $\Omega$  C<sub>1</sub>, C<sub>2</sub> 47nF C<sub>3</sub>, C<sub>4</sub> 68pF

CONTROL VOLTAGE (V)

and maintaining as close a ratio as possible between the R values. Frequency is approximately 1/3RC. Note that with the CR values necessary for 60° phase shift at a specific frequency, the output of each buffer stage is attenuated by about one half and hence the minimum gain of each stage must be > 2.

• An alternative arrangement is shown above right, using similar c.m.o.s. buffer inverters. In this case the resistor ratio is critical and theoretically for infinite gain amplifiers  $R_2 = R_1/2$  and a much better approximation to sinusoidal outputs is obtainable from each buffer, again phase shifted by  $60^{\circ}$ . Typical values  $R_1:100k\Omega$ ,  $R_2:33$  to  $39k\Omega$ , C:2700pF,  $V_{DD}-V_{SS}=6V$ , frequency 1kHz.

These buffers have gainfrequency responses which give higher gains for lower supply voltages. Typically 50dB at +3V up to 100Hz, and 30dB at +10V up to 100kHz. Hence since the gains are finite, then  $R_2$  must be less than  $R_1/2$ . But at the lower values of the supply range 3 to 15V, some flexibility of this value between each R2 is permitted. At higher levels the ratio is more critical, R2 may be replaced by f.e.ts employed as v.c.r. to obtain a restricted frequency range.

Further reading

Voltage controlled two-phase sawtooth oscillator, Wireless World, June 1973, p. 285.

AN-88 CMOS Linear Applications, National Semiconductor, p. 170.

Frequency controllable 3-phase sinewave generator, Electronic Engineering, July, 1974.

Cross references Set 11, card 6. Set 8, card 1.

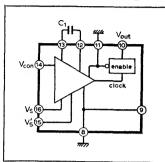

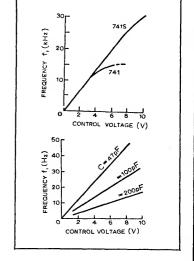

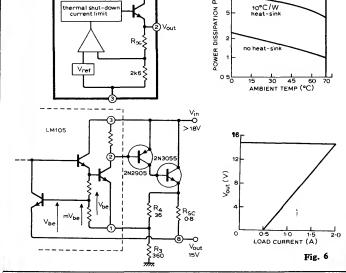

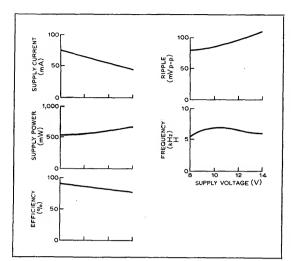

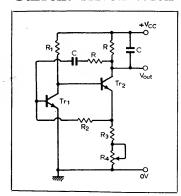

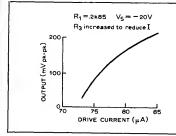

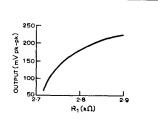

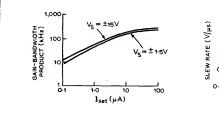

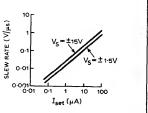

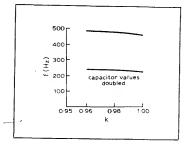

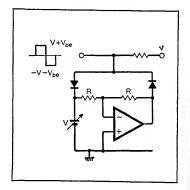

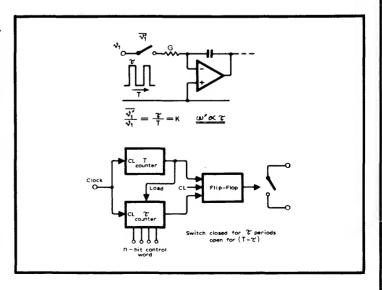

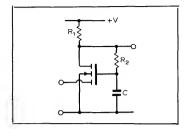

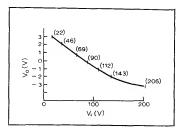

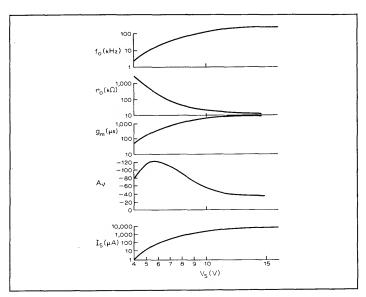

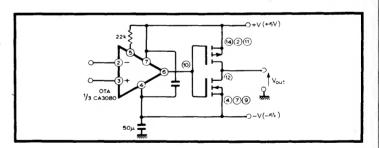

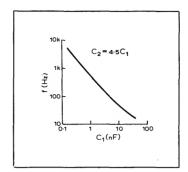

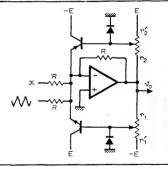

# Monolithic voltage-to-frequency converters

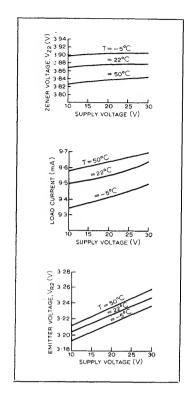

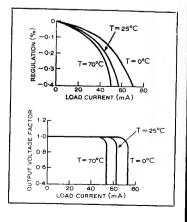

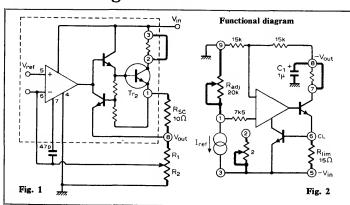

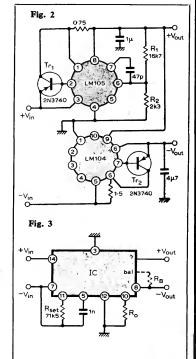

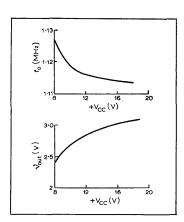

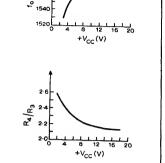

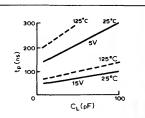

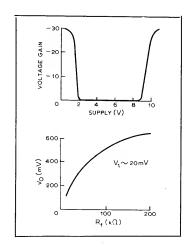

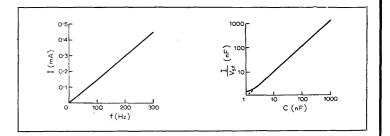

Typical data IC  $\frac{1}{2}$ SN74S124N C<sub>1</sub> 220pF  $V_s = V'_s + 5$ V d.c. Frequency range 0.7 to 1.8MHz (approx. linear)

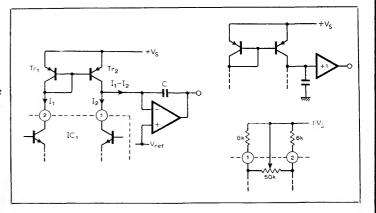

Circuit description

An emitter-coupled astable multivibrator uses a single capacitor for timing. The circuit has high switching speed because charge storage effects are avoided by using the transistors in a non-saturated mode. This circuit is the basis of the above medium-scale integration package, where variable frequencies are

obtained by charging the external capacitor at different rates via an internal voltage-controlled current source. The i.c. package contains two identical networks, but if only one is being used, it is essential that both ground connections (pins 8 & 9) are earthed to ensure earthing of the substrate and good isolation. The enable terminal

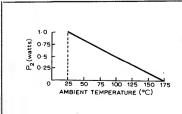

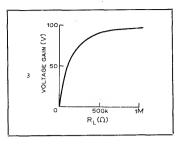

(no. 11) must be grounded for continuous output at the output terminal. Output is disabled if this terminal is taken to logic high or open-circuited. Graphs opposite indicate linearity over a restricted range for each capacitor value, and waveform deteriorates at very low values of C<sub>1</sub>, and thus at high frequencies.

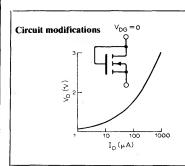

#### Circuit modification

• Emitter-coupled astable output swings are usually restricted. An additional output stage supplied via V's permits the output swing to be approximately 0V up to V's and hence t.t.l. compatibility is easily achieved, i.e. V's and Vs need not be the same.

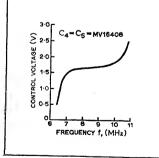

• Variable-capacitance diodes may provide a wider frequency range, depending on type (see over). Supply voltage 4.5 to 6.5V, frequency maintained constant

Components (circuit above) Supply  $\pm 10V$  IC<sub>1</sub> SH74S124N IC<sub>2</sub> LM301 R<sub>1</sub> R<sub>2</sub>  $10k\Omega$  R<sub>3</sub> R<sub>4</sub>  $100k\Omega$  C<sub>2</sub> C<sub>3</sub>  $1\mu$ F C<sub>4</sub> C<sub>5</sub> MV16408

IC<sub>2</sub> is connected as a non-inverting amplifier with a voltage gain of two, so that the biasing voltage in this case is twice the control voltage. This gain can be altered for appropriate voltage range. A claimed frequency range of 2 to 20MHz using varactors MV1403 and MC1456 for IC<sub>2</sub> is documented in the referenced literature.

Components (circuit right) IC<sub>3</sub> LM566, SE/NE566 General-purpose voltage-controlled oscillator. C<sub>T</sub> 4.7nF  $C_6$  0.047 $\mu$ F R<sub>8</sub> 4.7k $\Omega$  R<sub>T</sub> 10k $\Omega$  Maximum sweep rate 1MHz R<sub>T</sub> and C<sub>T</sub> are the frequency

range determining components. For a fixed value of  $C_T$  10:1 variation in frequency is possible via a variable input at  $V_{\rm control}$  which should be within the range 3 to 5.5V for  $V_{\rm cc} = \pm 6V$ .

The above values provide for a maximum free-running frequency of about 10kHz for  $Tr_1$  off. For  $V_s = -3V$ ,  $Tr_1$  is saturated, hence increasing timing capacitor 10 times, free-running frequency is then approximately 1kHz.

Control voltage measured between pins 8 and 5 should be in the range 0 to  $0.25\,V_{\rm cc}$ . (It is this voltage divided by R  $_{\rm T}$  which defines capacitor charging current.) Frequency is

$$\frac{2(V_{\rm ee}-V_{\rm control})}{R_{\rm T}C_{\rm T}V_{\rm ee}}$$

Further reading Klein, E. Medium-scale integration for instrumentation and control, *Semiconductors* (Motorola) vol. 2 no. 1 1971, p. 20.

Signetics: SE/NE566 function generator data sheet.

Cross references Set 17, card 3 Set 8, card 9

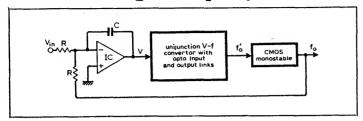

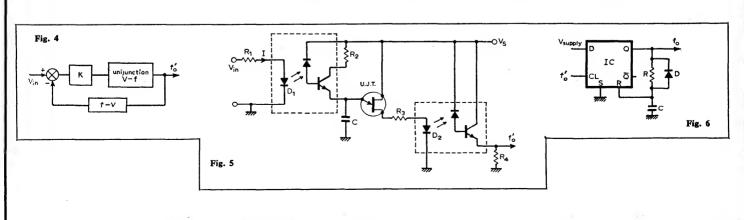

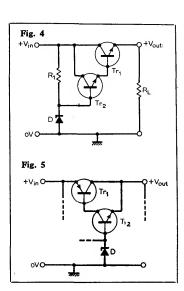

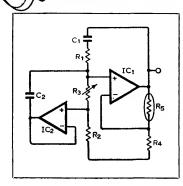

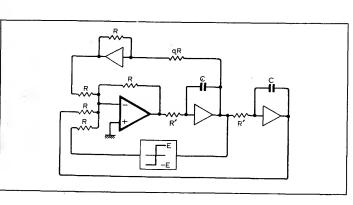

#### Linearized voltage-to-frequency converter

Components

R 100k $\Omega$ , C 0.22 $\mu$ F IC 741 Unijunction V-f'<sub>0</sub>—see over, centre. Monostable—see over, right V<sub>in</sub> 0 $\rightarrow$ -10V

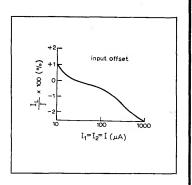

#### **Performance**

Graphs of f'<sub>o</sub> and f<sub>o</sub> are shown in Figs. 2 and 3. Graph of V against f<sub>o</sub>, corresponding to open-loop v-f conversion, is shown in Fig. 2. with V<sub>in</sub> against f<sub>o</sub> shown in Fig. 3. Linearity achieved was better than 0.5%—clearly much better than the open-loop performance.

#### System description

If the loop gain of a closed-loop system is high then the effect of non-linearities in the forward path is much reduced. In this case we have a highly non-linear V to fo converter and an integrator/error detector is then included to provide the feedback. In d.c. terms, the integrator can be regarded as having infinite gain since for finite input voltage the output

voltage after infinite time is infinite, ignoring the effect of saturation. Alternatively:  $\Delta V =$

$$1/RC\int_{0}^{T}V_{\rm in}dt+1/RC\int_{0}^{t}15dt$$

The steady-state condition of constant fo can only occur when V is constant and this occurs when  $\Delta V$  is zero i.e. when the integral of the input signal and the integral of the feedback signal exactly cancel. Hence exact correspondence between  $V_{in}$  and  $f_0$  can be expected if the integrator and feedback signal are "perfect". Immediate improvement in the system would be effected if an i.c. with much lower input current requirements were used e.g. 308. Further improvement would be obtained by the use of a low-loss capacitor. The c.m.o.s. monostable was included to give an output pulse train of well defined height and width and overall shape. A better f'o to fo converter could have been used. It should be noted that the overall characteristics are now dictated by the feedback signal and the integrator so that

forward path changes, causing changes in f<sub>0</sub>, will be completely cancelled, apart from transient effects. Changes in the shape of f<sub>0</sub>, e.g. impulse height and width, will however have an effect on f<sub>0</sub>, although not linearity.

#### System modification

Effectively, the combination of the monostable and integrator is an f'o to v converter. The system could therefore be changed to that shown in Fig. 4. K would be chosen to be sufficiently high such that the linearity of the overall system is equivalent to that of the f to v converter. This is only satisfactory if the shape of the f'o pulses is satisfactory.

#### **Element description**

The circuit of Fig. 5 shows the detail of the unijunction v to f converter (card 1) used. The opto-elements are included to show that their inherent isolating properties can be used not least to produce a very non-linear v to f'o characteristic. This is because D<sub>1</sub> requires approximately 1.6V to conduct and there is non-linearity in the

device current transfer ratio.

Resistor R<sub>2</sub> is included to protect the transistor and R<sub>4</sub> is large to produce a sufficiently large pulse to trigger the monostable. Resistor R<sub>1</sub> may be reduced to allow much lower input voltages to be used. The limit is set by the opto-diode input current. Any opto-isolator may be used e.g. TIL112.

Components  $R_1 2.2k\Omega$ ,  $R_2 1k\Omega$ ,  $R_3 100\Omega$   $R_4 10k\Omega$  Opto-isolators 4350 (Hewlett-Packard) U.j.t. 2N2646 V<sub>8</sub> 15V

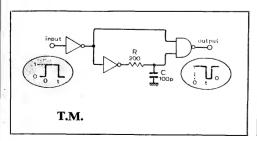

Circuit of Fig. 6 is the c.m.o.s. monostable used. It is identical in format to that described in set 18, card 8 but includes an extra diode to allow the capacitor to discharge closer to zero volts to improve linearity.

#### Components

$C 0.01 \mu F$

R 100kΩ C 2.2nF D 1N914 IC CD4013E

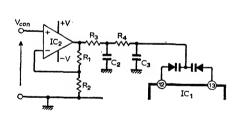

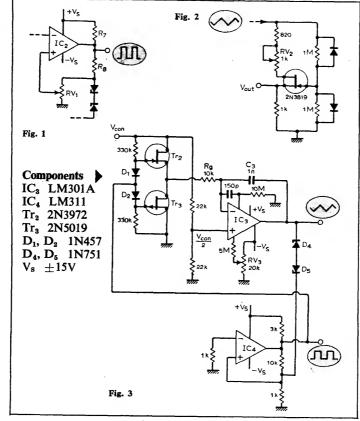

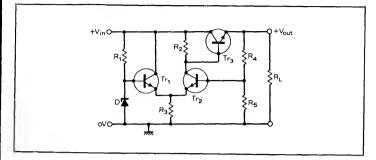

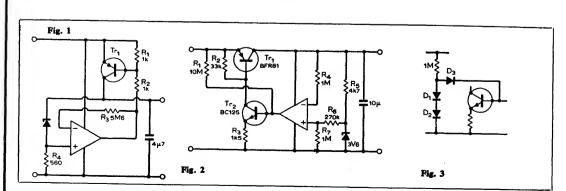

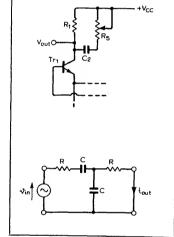

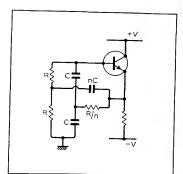

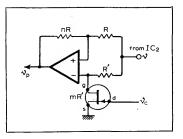

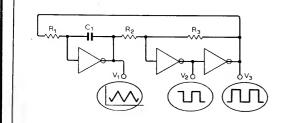

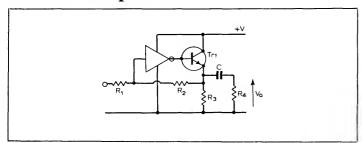

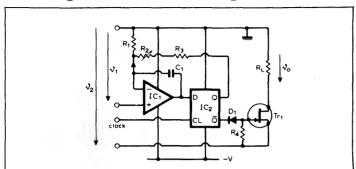

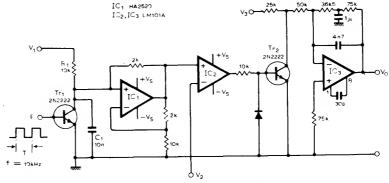

# Linear voltage-to-frequency converters

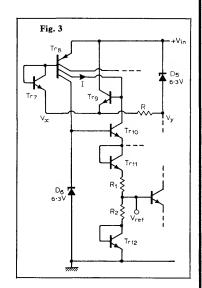

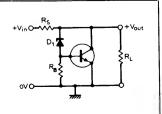

#### Circuit description

The circuit comprises an integrator whose output ramps toward positive and negative target values defined by diodes D<sub>2</sub> and D<sub>3</sub> i.e. the potential at the non-inverting input of comparator IC<sub>2</sub> is V<sub>D2</sub>+V<sub>D3</sub>+  $V_{BC}$  (or  $V_{D1}$ ) about  $\pm 9V$ . When the transistor is off (Vo2 negative), capacitor current

$$I = \frac{V_{\text{control}} \left( 1 - \frac{R_2}{R_1 + R_2} \right)}{R_3 + R_4}$$

(1)

When Tr<sub>1</sub> conducts, I is

$$I = -V_{\text{control}} \left( \frac{R_2}{R_1 + R_2} \right) / R_4 \quad (2)$$

For equal slopes at the triangular output, Vo1, the current magnitudes are equal, provided

$$\frac{R_1}{R_2} = 1 + \frac{R_3}{R_4}$$

$\frac{R_1}{R_2} = 1 + \frac{R_3}{R_4}$ If Vo<sub>2</sub> is positive, Tr<sub>1</sub> is on, and integrator output rises towards +9V at which level the comparator IC2 switches over to make Vo2 negative, bringing Tr<sub>2</sub> out of conduction. C<sub>1</sub> charges according to the first equation, and integrator output ramps towards -9V, when comparator again changes state. Components C<sub>2</sub>, R<sub>5</sub>, R<sub>6</sub> form a phase-advance network to compensate for the switching delays of IC2 and Tr1 at the higher frequencies. The invert mode of Tr<sub>1</sub> provides a very low collector-emitter drop (few millivolts), i.e. the effect on the second equation is neglected. Linearity is better than 0.5% over the range of control

voltage, 0.1V to 8V, based on deviation from 6V value.

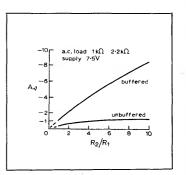

#### Component changes

This slew rate is typically  $10V/\mu s$ . If 741 used, slew rate  $(0.5V/\mu s)$  restricts higher frequency to which linearity is maintained (see graph).

Range of C<sub>1</sub>: Typically 47 to 200pF. Frequency variation shown on graphs. Frequency is power supply dependent, hence need for good stability of supply.

Typical performance data Supply ±15V IC<sub>1</sub> 741S IC<sub>2</sub> LM311 Tr<sub>1</sub> ME4002  $R_1$  68k $\Omega$ ,  $R_2$  22k $\Omega$ ,  $R_3$  33k $\Omega$  $R_4$  15k $\Omega$   $R_5$ ,  $R_7$  3.3k $\Omega$  $R_6$  12k $\Omega$   $R_8$  4.7k $\Omega$  all  $\pm 5\%$ C<sub>1</sub> 100pF C<sub>2</sub> 1nF D<sub>1</sub> 1N914 D<sub>2</sub>, D<sub>3</sub> reference diodes 6.8V e.g. BZY88 V<sub>control</sub> range 0 to 10V Triangular output ±8V peak Frequency range 30Hz to 33kHz

Vary mark/space ratio of output at  $V_{O_2}$  by  $R_2/R_1$  ratio change; this also modifies frequency. Range of  $R_2$ ,  $R_1$  22 to  $68k\Omega$ Range of mark/space 1:1 to 1:3.

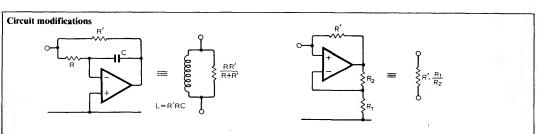

#### Circuit modifications

• A variable output voltage is obtainable via the circuit shown in Fig. 1. Comparator hysteresis can be changed by varying the fraction fed back via a potentiometer RV<sub>1</sub>. This will control the output

amplitude. The triangular output is shaped by the circuit of Fig. 2. Potentiometer RV<sub>2</sub> is adjusted for a minimum even-harmonic content, to provide an approximate cisoidal wave form at Vout.

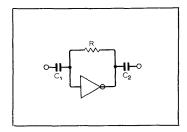

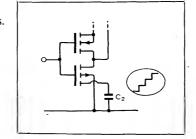

The field-effect transistors of Fig. 3 provide a similar switching action to Tr<sub>1</sub> in first circuit to provide the integrator capacitor current charging paths. IC<sub>3</sub> as an integrator employs a speed-up network of 150pF in series with  $10M\Omega$ resistor.

Transistors Tr<sub>2</sub> and Tr<sub>3</sub> controlled by square-wave output from the Schmitt circuit of IC4. When Tr2 is on, Tr3 is off and  $C_3$  charges via  $Tr_2$  and  $10k\Omega$ resistor. With Tr<sub>2</sub> off, and Tr<sub>3</sub> on, current reverses through the capacitor with magnitude defined by  $V_{\text{control}}/2R_9$ . RV<sub>3</sub> should be adjusted to provide a symmetrical square-wave output when V<sub>control</sub> is 5mV. Input control voltage range: 5mV up to 5V. Frequency range 10Hz to 10kHz.

Further reading

Wright, M.J. Linear voltage to frequency converter, Electronic Engineering, July 1973. Linearize your v-f converter, Electronic Design, Nov. 1973. Applied Ideas, Electronic Engineering, Jan. 1975, p. 17. Linear Integrated Circuits, National Semiconductor, 1972, p. 255.

Cross references Set 3, cards 1, 5, 11 Set 17, card 3

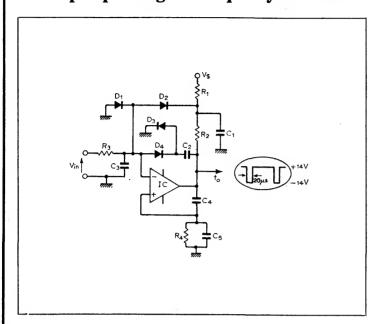

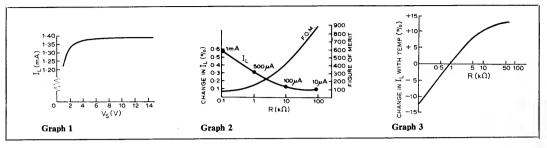

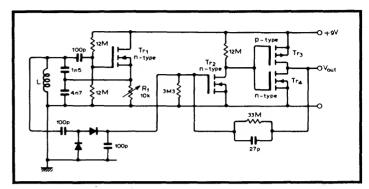

#### Diode-pump voltage-to-frequency converter

Circuit description Elements  $R_1$ ,  $R_2$ ,  $D_1$ ,  $D_2$  and C<sub>1</sub> are not basic to the action of this circuit and will be ignored initially. Suppose the i.c. output is sitting at +14V. Then C2 will have been charged to this level via D<sub>3</sub>. However as C<sub>3</sub> charges via R<sub>3</sub> under the influence of Vin, the negative terminal of the i.c. eventually reaches 0V and the amplifier output swings negative. The network comprising C<sub>4</sub>, R<sub>4</sub> and C<sub>5</sub> provides sufficient positive feedback to make this swing very rapid—hence the use of a high speed op-amp. Capacitor C<sub>2</sub> then deposits its charge via D<sub>4</sub> into C<sub>3</sub> in a diode pump fashion thereby lowering the voltage across C<sub>3</sub>. However the positive feedback network consists of elements with a short time constant and the voltage on the positive terminal quickly becomes less negative than the negative terminal voltage and so the amplifier voltage swings back to +14V. In the -14V period the circuit is acting rather like a monostable, the delay being fixed by the C<sub>4</sub>, R<sub>4</sub>, C<sub>5</sub> network and by the R<sub>3</sub>, C<sub>3</sub> network. Because there is again positive feedback the rising edge will be

equally sharp but the period will be difficult to define accurately, partly because of the complexity of the CR networks and partly because two voltages both going in the same direction (positive) are being compared. This, however, is not serious since the pulse width does not affect the amount of charge on C<sub>2</sub>, and it is this charge which is being balanced by the current in the input network. The maximum frequency we obtained was close to the limit of the op-amp but the markspace ratio could have been made even lower if required by reducing C<sub>3</sub>, R<sub>3</sub> or lengthening the time constant of C<sub>4</sub>, R<sub>4</sub>, C<sub>5</sub>. The network comprising R<sub>1</sub>,

#### Circuit modifications

• A high-speed comparator would be preferable to an op-amp which was used in our experiments.

R<sub>2</sub>, C<sub>1</sub> and D<sub>2</sub> prevents the device from locking into a

an input voltage (positive).

by a negative input voltage.

saturated condition by too large

Diode  $D_1$  prevents the negative

input terminal being overdriven

• The pulse width does not theoretically affect the result

#### **Components**

Supplies  $\pm 15V$ IC 748C R<sub>1</sub> 12k $\Omega$ , R<sub>2</sub> 3.9k $\Omega$ R<sub>8</sub> 10k $\Omega$ , R<sub>4</sub> 4.7k $\Omega$ C<sub>1</sub> 4.7 $\mu$ F, C<sub>2</sub> 1nF C<sub>3</sub> 33 $\mu$ F, C<sub>4</sub> 56pF C<sub>5</sub> 500pF D<sub>1</sub> to D<sub>4</sub> 1N914

#### Performance

V<sub>in</sub>: 0 to +4.00V Output pulse train: pulse width about 20 $\mu$ s swinging from +14V to -14V with a maximum frequency of around 14kHz, corresponding to a mark-space ratio approaching 3:1. Linearity better than 0.3% over two decades.

but the pulse height does. A c.m.o.s. buffer amplifier could be included to give a well defined output pulse height—see reference 2.

• An alternative approach to the pulse height problem is to use internal clamping of the output level—see references 3.

#### References

- Pease, R. Ultra-linear voltage-to-frequency converter, *Electronic Engineering*, March 1971.

- 2 Set 3 (waveform generators) card 11.

- 3 Set 3, card 1. Set 2, card 1.

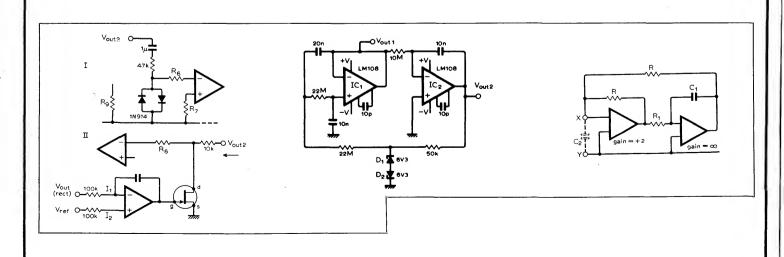

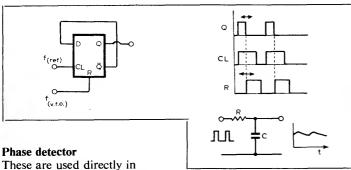

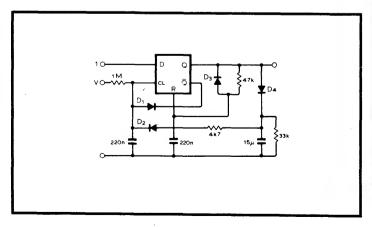

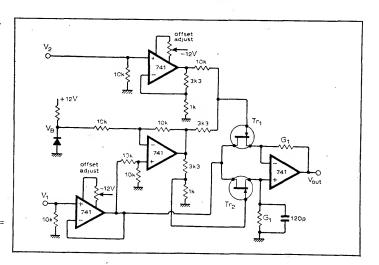

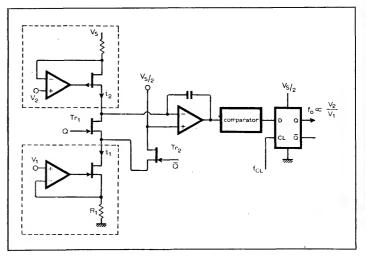

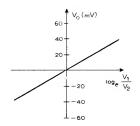

# Differential input voltage-to-frequency converter

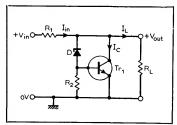

#### Circuit description

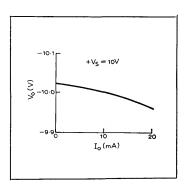

The above circuit is of a form published by Woodward but with what appear to us as corrections, although we have to admit to not achieving the performance claimed in his article, viz linearity better than 0.05% from 10Hz to 10kHz. The results we achieved are shown roughly in Fig. 2, measured linearity being 0.15% over the two decades, 100Hz to

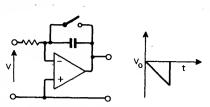

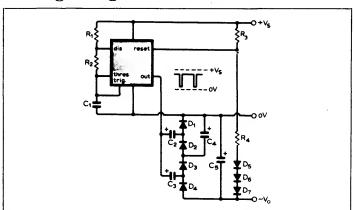

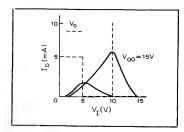

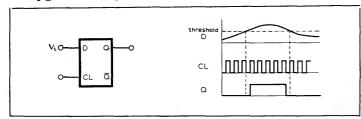

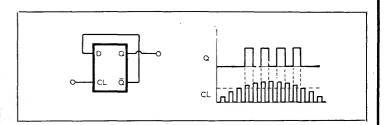

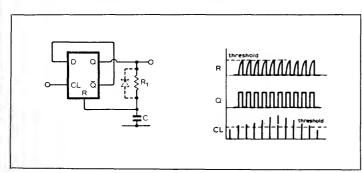

Pin c of IC<sub>2</sub> is the R (reset) terminal and its action is not necessary in a brief explanation. Pins a and b are the trigger and threshold terminals of the i.c. When the C2 capacitor voltage goes below the trigger potential,  $V_s/3$ , the output swings high, and when the voltage exceeds the threshold voltage,  $2V_s/3$ , the output swings low-see waveforms of Fig. 3.

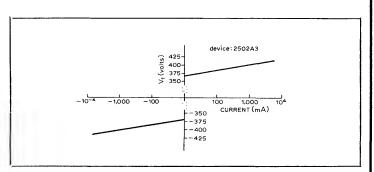

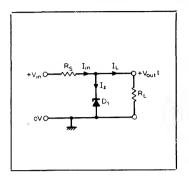

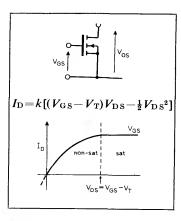

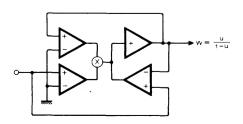

The basic principle is that of charge dispensing in which a current proportional to a voltage is balanced by the periodic charging of a capacitor to a precise voltage. In this case, the current through the f.e.t. is fixed by the input voltage at  $V_{in}/R_{in}$ . This current flows for time T as a result of the charging of C<sub>2</sub> from V<sub>s</sub>/3 to  $2V_s/3$ . Thus

$$\frac{V_{\rm in}}{R_{\rm in}} T = C_2 \frac{V_{\rm s}}{3}$$

$f_0 = \frac{3V_{\rm in}}{R_{\rm in}C_2V_{\rm s}}$ and

This expression is valid so long as T is large compared with the pulse width.

When the output goes high C2 charges via R<sub>3</sub> and D<sub>2</sub> from

$V_s/3$  toward  $V_s$ . During this period  $D_1$  is reverse biased and at the same time C<sub>1</sub> is providing some current to the f.e.t. When C<sub>2</sub> reaches 2 V<sub>8</sub>/3 the output goes low, D1 conducts, C<sub>1</sub> and C<sub>2</sub> share the charge on C<sub>2</sub> and the parallel combination discharges linearly through the f.e.t. Diode D<sub>2</sub> is reverse biased in this period.

The sharing of the charge between C<sub>1</sub> and C<sub>2</sub> causes the sharp drop in the C2 voltage when  $2V_s/3$  is reached. The discharge is linear because the f.e.t. current is fixed by the input voltage.

The results obtained required adjusting of the op-amp offset voltage to zero. Common-mode rejection ratio is independent of input resistor match and is dictated by the op-amp used. However, common-mode voltage should not exceed  $\pm 2V$ .

#### Component changes

The charging time depends on  $C_2R_3$  and should be short without R<sub>3</sub> being so low as to overload IC2. This is not difficult to achieve since it is the open collector terminal which is used to charge C<sub>2</sub>. Capacitor C<sub>1</sub> serves to cut off D<sub>1</sub> whilst C<sub>2</sub> is charging, so its value is not critical. Generally speaking though it should be less than C<sub>2</sub> to minimize the drop in C2 voltage when D1 starts conducting again, thereby keeping the slope of the downwards ramp as large as possible and clearly defining the time at which the voltage drops below  $V_s/3$ . Actually,  $C_1$ and D<sub>1</sub> can be removed altogether without complete failure of the circuit, although linearity and output pulse shape

Components

Supplies  $\pm 15V$  IC<sub>1</sub> 741, IC<sub>2</sub> NE555

Tr 2N5457

R<sub>1</sub> 270Ω

$R_2 1.2k\Omega$

$R_3$  47 $\Omega$

C<sub>1</sub> 1nF

$C_2$  22nF

D<sub>1</sub>, D<sub>2</sub> 1N914

are affected.

Diodes D<sub>1</sub> and D<sub>2</sub> can be any general-purpose diodes unless very high speed operation is required.

Reducing the values of the op-amp input resistors and choosing a suitable op-amp will allow values of Vin in the millivolt region to be used to give the same output frequencies.

#### Circuit modifications

Any circuit which will successfully draw constant current from the junction of C<sub>1</sub> and D<sub>1</sub> will produce the same result and such a circuit is shown in Fig. 4. The photodiode current is proportional to light intensity so an intensity-to-frequency converter would be produced by this arrangement. The differential input aspect is lost, however, unless one puts a second photodiode, connected the opposite way round, across the one shown.

#### Reference

Woodward, W. S. Simple 10kHz voltage-to-frequency converter features differential inputs, EDN, Oct. 20, 1974, p. 86.

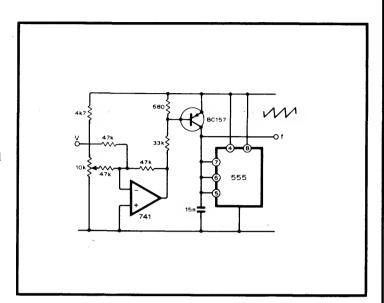

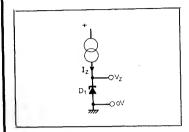

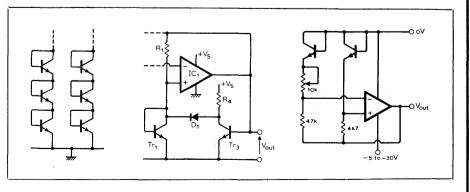

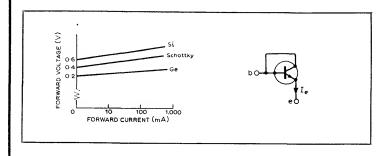

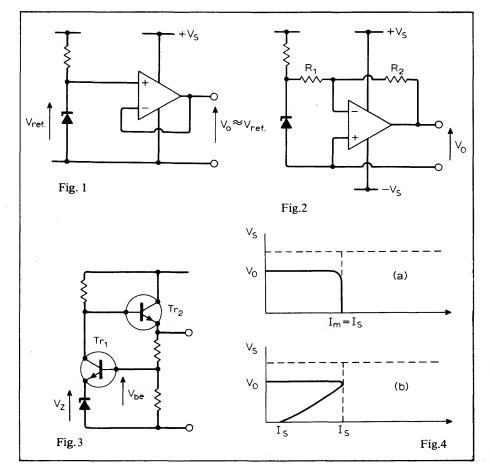

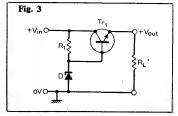

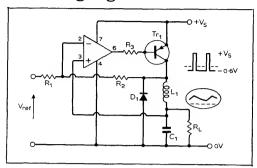

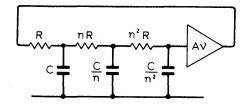

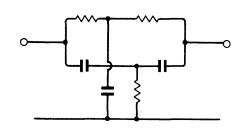

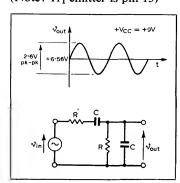

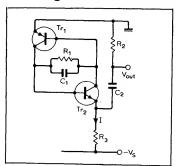

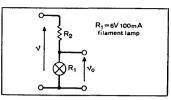

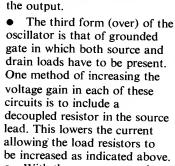

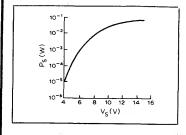

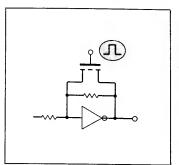

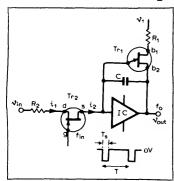

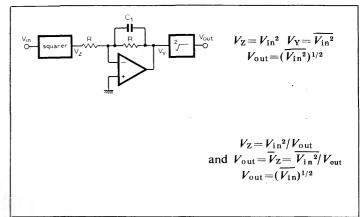

Most of the circuits described have been aimed at linearizing the v-f conversion, as in measurement of modulation systems. Sometimes it is required to have a converter in which the v-f conversion is highly non-linear with the frequency following, for example, an exponential or logarithmic function or sharply changing at some threshold voltage. The circuit indicates a simple way of changing the frequency over a claimed five-decade range.

A linear voltage variation is applied to the base-emitter junction of a transistor to charge a capacitor. The capacitor forms part of an

astable circuit based on the well-known 555 timer, with a sawtooth waveform generated across the capacitor swinging between V/3 and  $2V_s/3$ . The reference indicates additional components to set the frequency to zero for V=0 and for buffering the output waveform. More generally a linear v-f converter is combined with a non-linear amplifier whose non-linearity is predictable, rather than introducing non-linearity into the conversion process itself.

#### Reference

Brice, J. L. Voltage-controlled ramp generator, *Wireless World*, June 1976, p. 72.

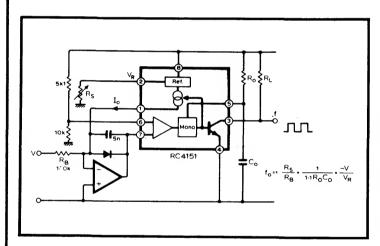

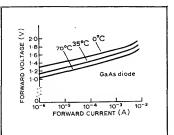

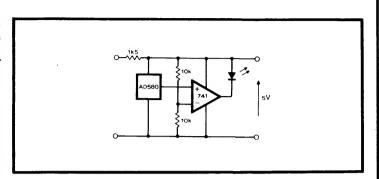

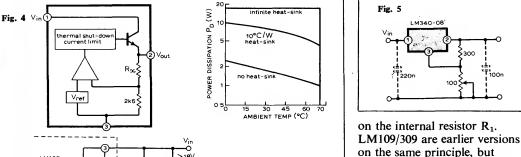

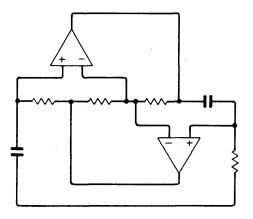

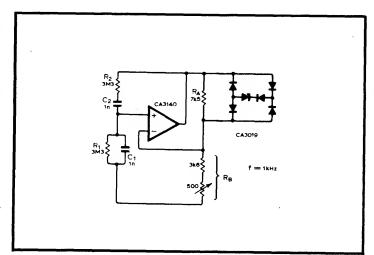

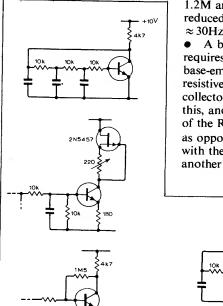

The new generation of linear integrated circuits includes complete v-f modules that will compete with the hybrid and modular versions for many applications. One such monolithic device RC4151 is in line of succession to the 555. It includes a monostable comparator and output stage, but adds a switched current generator. It can be used without additional active devices, but for improved linearity is combined with an op-amp to form a chargebalancing system. The input

current to the summing junction is balanced by the constant-height constant-width current pulses returned by the monostable ensuring a linear relationship. A zero-offset voltage fed to the non-inverting terminal ensures that  $f\rightarrow 0$  as  $V\rightarrow 0$ . Resistor  $R_s$  sets the scale-factor for 0-10kHz corresponding to  $0\rightarrow 10V$ .

#### Reference

Cate, T. IC V-f converters readily handle other functions such as f-V, A-D, *EDN*, Jan. 5, 1977, pp. 82–6.

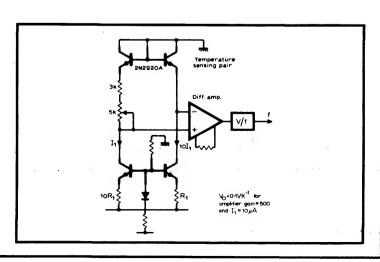

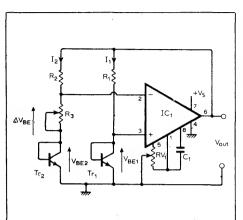

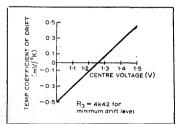

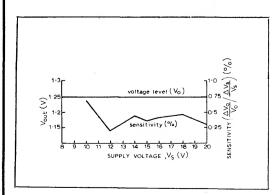

The same article shows amongst other applications a linear thermometer, with some similarity to the band-gap reference circuits of set 23. The temperature-sensing pair are forced to operate at a 10:1 ratio of collector currents giving a  $\Delta V_{\rm BE}$  that is a controlled linear function of temperature. The precise

scaling factor is set by the  $5k\Omega$  resistor. The amplifier requires to be a true differential input amplifier of controlled gain. Again the overall function is split into two parts: a linear v-f converter, and a separate circuit to provide the linear or nonlinear response. It would be proper to describe this as a T-V-f converter.

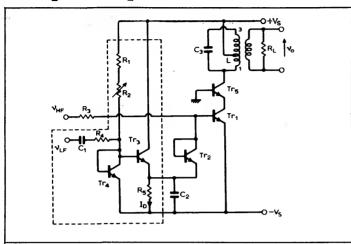

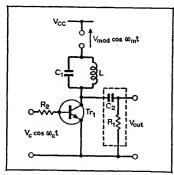

#### Set 22: Amplitude modulators

The term amplitude modulation here includes modulation with either one or two sidebands, with or without a carrier present, by one of four methods—multiplication, switching, non-linearity, or direct tuned-circuit modulation in a class C amplifier. The circuits using 741s are limited to use with carrier frequencies of a few tens of kilohertz, but two other i.c. designs—the modulated crystal osillator of page 27, the "micropower" circuit of page 32 and those of page 24—operate with carriers of the order of megahertz. And examples of v.h.f. modulators are given on page 33.

The i.c. modulator of page 24 can double as a withcarrier or suppressed-carrier circuit, and uses a biased gating-control input for the modulation. Balanced i.c. modulators appear in place of circuit modifications on

this page (see also page 31).

Operating conditions for the lower circuit on card 7, originally omitted, have been added and further reading for the bridge modulator added.

Background article 22

IC package modulators 24

Linear amplitude modulator 25

Modulator using precision rectifiers 26

Modulated crystal oscillator 27

Diode bridge modulators 28

Single-sideband generation 29

FET modulators 30

Long-tailed pair modulators 31

Micropower amplitude modulator 32

Direct tuned-circuit modulator 33

Up-date circuits 34

# **Amplitude modulators**

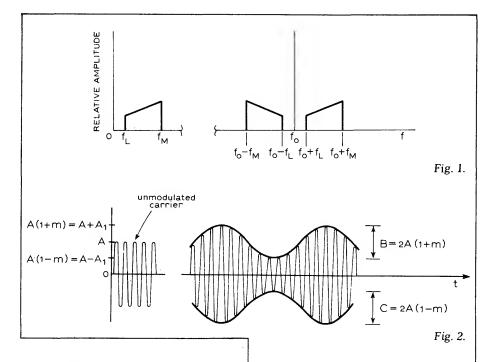

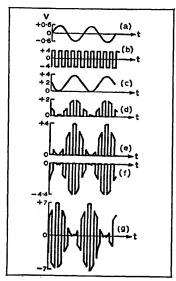

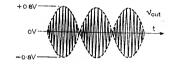

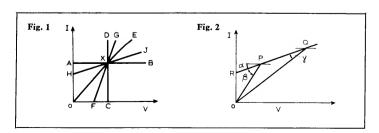

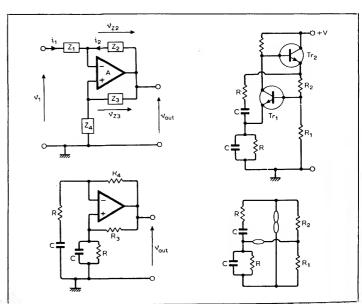

If the amplitude of a high-frequency sinusoidal carrier,  $c(t) = A \cos \omega_0 t$  is made to vary in sympathy with the instantaneous value of a low-frequency signal x(t) an amplitude-modulated signal is generated which has a spectrum concentrated in the vicinity of the unmodulated carrier frequency,  $f_0$ . The effect is to shift, or frequency-translate, the spectrum of the modulating signal to produce a pair of sidebands symmetrically disposed with respect to  $f_0$  as shown in Fig. 1. The resulting wave may be described by:  $y(t) = [A + x(t)]\cos \omega_0 t$ , so if, for example, x(t) is a pure tone modulating signal represented by  $x(t) = A_1 \cos \omega \cdot t$  the a.m. output becomes  $y(t) = [A + A_1 \cos \omega_1 t] \cos \omega_0 t$ may be written  $y(t) = A[1 + m\cos \omega_1 t]\cos \omega_0 t$  where  $m = A_1/A$  is the modulation index, or modulation depth, and has a value ≤1 if over-modulation is to be avoided.

The amplitude modulated waveform is shown in Fig. 2, and if this is displayed on an oscilloscope the modulation index may be found from m = (B-C)/(B+C). As well as measuring the modulation index, the oscilloscope may be used to examine the linearity of the modulation process if it has an X-Y facility. If the amplitude modulated wave is applied to the Y-amplifier and the low-frequency modulating signal applied to the X-amplifier a Lissajous figure of y(t)/x(t) is obtained as shown in Fig. 3.

The above process is what is generally accepted as understood when referring to a.m. However a family of processes may together be considered as amplitude modulation techniques which include

- a pair of sidebands with carrier (a.m.)

- a pair of sidebands without carrier (d.s.b. or d.s.b.s.c.) or with diminished carrier (d.s.b.d.c.)

- an upper or lower sideband without carrier (s.s.b.) or with diminished carrier (s.s.b.d.c.)

- a pair of single sidebands with independent modulation (i.s.b.)

- one sideband, carrier and a vestige of the other sideband (v.s.b.)

In general, the above systems depend in some way on the use of four basic

methods of producing amplitude modulation.

- analogue multiplication

- chopper modulation

- non-linear-device modulation

- direct tuned-circuit modulation

Except for the last method listed, modulation is normally performed at low power levels and the required output power obtained by class-B amplification of the modulated signal.

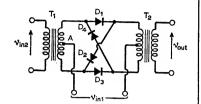

Analogue modulation, or multiplication, is obtained by applying the modulating signal and the carrier to a circuit providing an output which is a function of the product of its inputs. Output from the multiplier or balanced modulator is ideally a d.s.b.s.c. signal. This arrangement is often convenient for producing an s.s.b.s.c. signal by removing the unwanted sideband and any residual carrier by means of band-pass sideband filter.

Many multipliers or balanced modulators are available in the form of purpose-designed integrated circuits for operation at carrier frequencies of at least 100MHz. Depending on the nature of the modulating signal, the carrier

A(1+m)

$\infty(t)$

A(1+m)

Fig. 3.

linear modulation

non-linear modulation

Chopper modulation is obtained by chopping the modulating signal at the carrier rate, using either a sinusoidal or a square-wave carrier, and then passing the resulting wave through a band-pass filter centred on the carrier frequency.

The bandpass filter will normally remove the component at the modulating frequency as well as the sidebands centred on the harmonics of the carrier frequency. To ease the requirements of the band-pass filter a balanced chopper modulator removes the low-frequency modulating signal component. The carrier-driven switches are normally realized using diode bridges or field-effect transistors.

Modulation using a non-linear device is achieved by adding the modulating-and carrier-frequency components and then passing the resultant through a bandpass filter centred on the carrier frequency to extract the a.m. signal. The non-linear device should have non-linearity not exceeding second-order and the highest significant modulation frequency should not exceed one-third of the carrier frequency.

Direct tuned-circuit modulation is achieved by controlling the voltage across a parallel-tuned circuit, tuned to the carrier frequency, by means of the modulating signal and pulsing the tuned circuit at the carrier rate with a high-power, class-C amplified carrier pulse. If modulating frequency is too high its rate of increase can be such as to cause the envelope of the a.m. wave to become distorted due to the failure to follow the modulation.

The modulation techniques discussed above which use band-pass filters must provide a filter bandwidth suited to the transmission of the desired signal whilst rejecting all unwanted components. For a.m. and d.s.b. this bandwidth must be

twice the highest modulating frequency and for s.s.b. it must be equal to the bandwidth of the modulating signal. In virtually all these cases the sharp cut-off required from the bandpass filter is only obtainable if the centre frequency of the filter is relatively low. Normally the filtration is achieved in the region of 50Hz to about 1MHz and the resulting modulated wave heterodyned, or frequency translated, to the required carrier frequency for transmission.

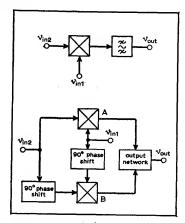

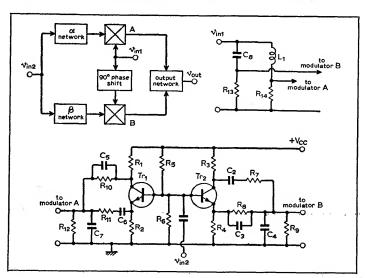

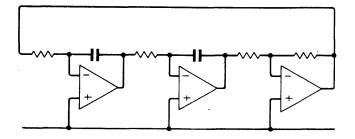

Another way is the phasing method of generating an s.s.b. signal which avoids the problems associated with filter design, but replaces them with the problem of designing a pair of networks (A and B) which are required to maintain a constant 90° phase difference between their outputs whilst their output amplitudes are held constant over the bandwidth of the modulating signal. Selection of either sideband is achieved by reversing the output from one of the balanced modulators or

by reversing the phase of either the carrier or the modulation to one balanced modulator. Because of the relative ease of inverting an audio signal, the modulating signal reversal is normally the simplest to accomplish in practice.

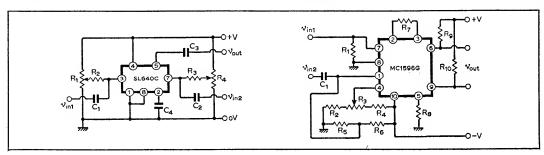

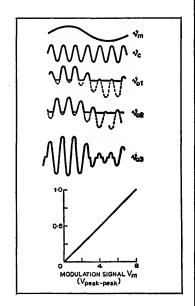

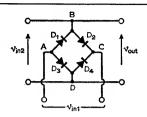

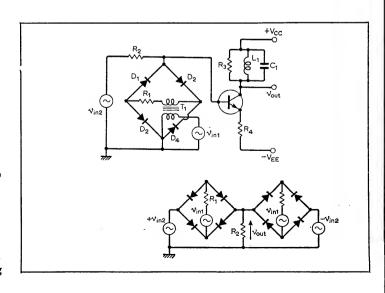

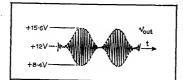

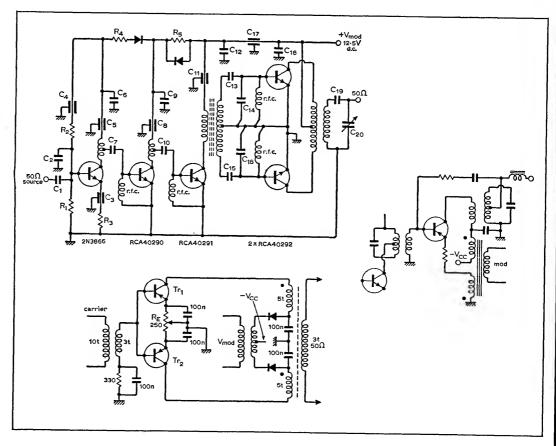

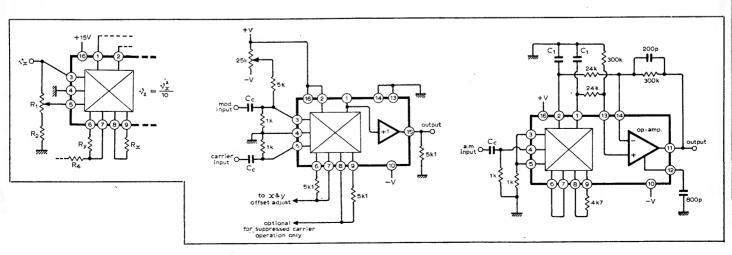

#### I.C. package modulators

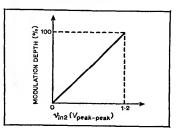

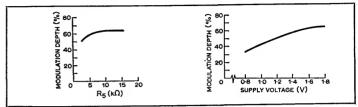

Typical performance Supplies  $\pm 10$ V, 10mA IC<sub>1</sub> MC1445L R<sub>1</sub> 47 $\Omega$  R<sub>2</sub> 4.7k $\Omega$ , R<sub>3</sub> 220 $\Omega$  C<sub>1</sub>, C<sub>2</sub> 100nF Amplitude modulator V<sub>G</sub> 2V d.c. v<sub>in1</sub> (carrier) 130mV pk-pk  $f_c$  1MHz v<sub>in2</sub> (modulation) 1.3V pk-pk  $f_m$ . 10kHz, to produce maximum useful modulation depth of  $\approx 78\%$ .

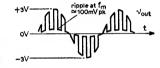

v<sub>out</sub> (pin 1 or 7) 800mV pk-pk unmodulated, see waveform opposite.

Balanced modulator

V<sub>G</sub> 2.5V d.c. to balance out carrier

v<sub>in1</sub> (carrier) 130mV pk-pk

f<sub>c</sub> 1MHz

v<sub>in2</sub> (modulation) 2.4V pk-pk

(max)

f<sub>m</sub> 10kHz

v<sub>out</sub> (pin 1 or 7) see waveform opposite.

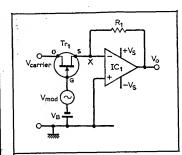

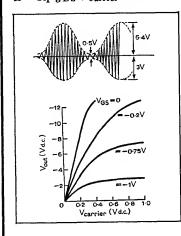

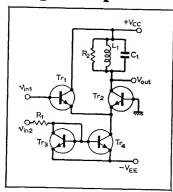

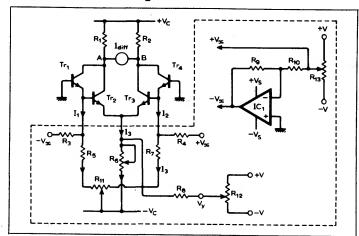

#### Circuit description

Many integrated circuit packages are available either in the form of purpose-designed modulators for producing a.m. or d.s.b. outputs or in the forms which can be readily adapted to these applications. An example of the latter type is the gate-controlled, twochannel-input wideband amplifier shown. This integrated circuit consists of a pair of differential-input amplifiers having a constant current switched between them under the control of a gating signal which cuts off one amplifier when the other is conducting. The output from each of these amplifiers is available via low-outputimpedance Darlington emitter followers. Although the gating signal would normally be at t.t.l.-compatible logic levels, the characteristics of the gate circuit allows the i.c. to be used as an amplitude modulator

when connected as shown. Although the voltage/gain/ gate voltage characteristic is far from linear over the full gate voltage range, it is virtually linear over a range of a few hundreds of mV with respect to a suitable d.c. bias. This bias is obtained by connecting a coarse/fine control (R<sub>2</sub>, R<sub>3</sub>) between the gate (pin 2) and ground. The low-frequency modulating signal is superimposed on this bias by coupling it to the gate through C2 and the carrier input is coupled via C1 and R1 to either of the input channels, pins 5 or 6 (as shown) or pins 3 and 4 (unused in circuit shown). The amplitude modulated output is available at either output, pin 1 or pin 7. With defined input signal levels, the output modulation depth may be varied using  $R_2$  and  $R_3$ .

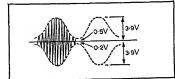

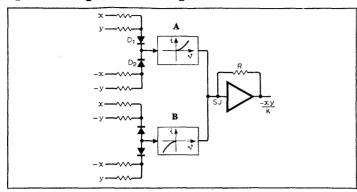

A double-sideband suppressedcarrier signal may be produced by applying the carrier simultaneously to both channels of the input differential amplifiers which then have their outputs cross-coupled. The resulting balanced modulator is as shown. but with pin 5 earthed and the junction of R<sub>1</sub> and C<sub>1</sub> taken to pins 6 and 3. If the carrier has sufficient amplitude to switch these channels completely off and on, the modulating signal is switched between the channels at the carrier frequency, which is equivalent to multiplying the modulating signal by a switching function—the required condition for producing a pair of side-frequencies and suppressing the carrier. If a reduced-amplitude carrier is required, this can be produced by slightly changing the d.c. bias applied to the gate terminal by means of R<sub>3</sub>.

Component changes

Useful range of supply ±4 to

12V

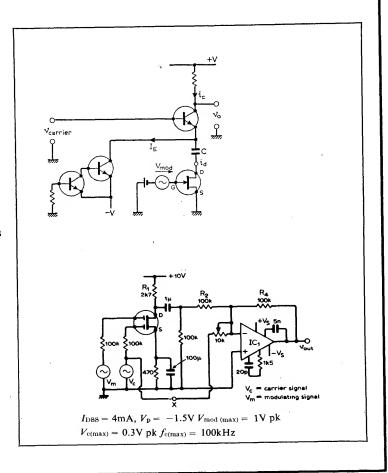

Maximum useful carrier input ≈280mV pk-pk producing unmodulated carrier output of  $\approx 3.3V \text{ pk-pk}$  $f_c(\text{max}) \approx 75\text{MHz}$ Maximum load current≈25mA. Examples of integrated circuits purpose-designed as balanced modulators are the MC1596G and the SL640C. These packages are essentially intended to replace diode-bridge or ring modulators with transistor double-balanced modulators to overcome the disadvantages of the former type of less than unity gain the need for a high level signal at one input and the need to use up to three transformers. The inherently good matching of the monolithic transistors ensures that excellent carrier suppression is obtained with little need for balancing by external components when the

devices are used as doublesideband suppressed-carrier generators.

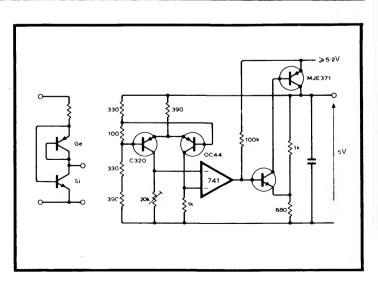

An arrangement of the SL640C for this purpose is shown Typically, V = +6V,  $R_1$   $R_4$  $10k\Omega$ , R<sub>2</sub> R<sub>3</sub> 330k $\Omega$ , C<sub>1</sub> C<sub>2</sub> and C<sub>3</sub> should have low reactance compared with the source and output resistance, except for high frequency applications (i.e. fc approaching 75MHz) where the modulation source resistance should be low and C2 of comparable reactance C<sub>4</sub> is a base-decoupling capacitor and must have a very low reactance at all frequencies used to minimize carrier and modulation feed-through. Resistors R<sub>1</sub> and R<sub>2</sub> are adjusted to minimize modulation and carrier leakage respectively. The circuit below shows the MC1596G used as an amplitude modulator.

Further reading

3.9k $\Omega$ , C<sub>1</sub> 1 $\mu$ F.

Microelectronics Databook: MC1445, MC1596 data sheets and AN-475, 2nd edition, Motorola 1969.

Integrated Circuit Databook, Plessey 1973. pp.103-5.

SL600-Series Application Manual, 2nd edition, Plessey 1974, pp. 29-34.

Typically  $V\pm 8V$ ,  $R_1$  47 $\Omega$

$R_3$  470 $\Omega$ ,  $R_8$  6.8k $\Omega$ ,  $R_9$   $R_{10}$

$R_2$ ,  $R_4$ ,  $R_5$ ,  $R_6$ ,  $R_7$  1k $\Omega$

Cross reference Set 21, card 2.

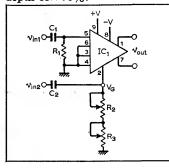

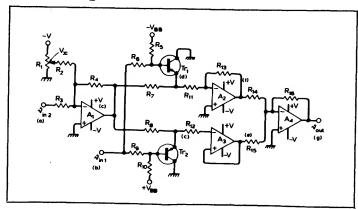

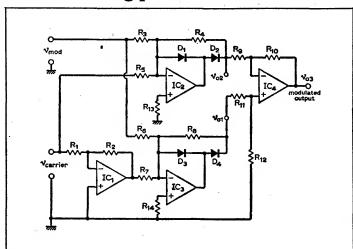

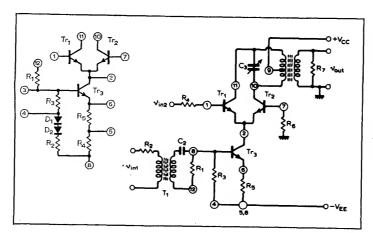

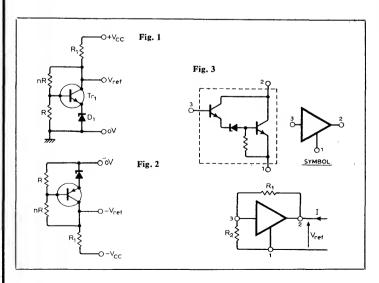

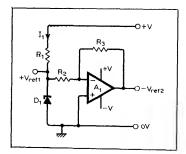

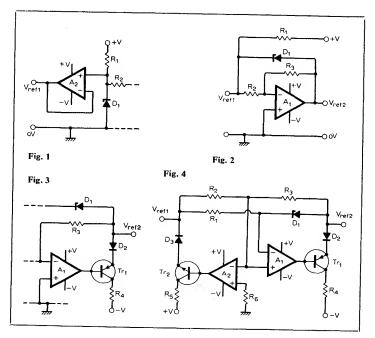

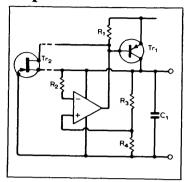

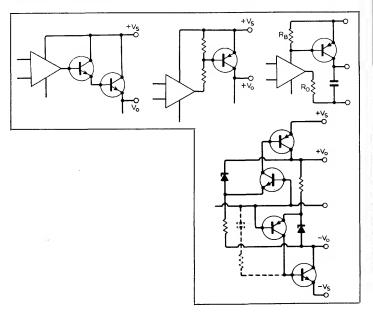

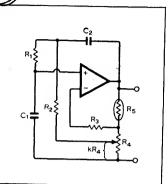

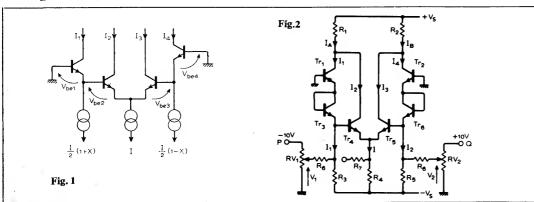

#### Linear amplitude modulator

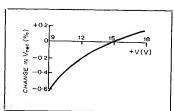

Typical performance Supplies  $\pm 15V + 7.5 \text{mA}$ , -9.3 mA,  $V_{\text{BB}} \pm 5V 0.75 \text{mA}$  A<sub>1</sub> to A<sub>4</sub> 741 R<sub>1</sub>, R<sub>8</sub>, R<sub>7</sub>, R<sub>8</sub>, R<sub>11</sub>, R<sub>12</sub>  $10 \text{k} \Omega$  R<sub>2</sub>  $100 \text{k} \Omega$  R<sub>4</sub>  $33 \text{k} \Omega$  R<sub>5</sub>, R<sub>10</sub>  $4.7 \text{k} \Omega$  R<sub>6</sub>, R<sub>9</sub>  $1.5 \text{k} \Omega$  R<sub>18</sub>, R<sub>14</sub>, R<sub>15</sub>  $22 \text{k} \Omega$  R<sub>16</sub>  $39 \text{k} \Omega$  Tr<sub>1</sub> BC125 Tr<sub>2</sub> BC126 V<sub>x</sub> -5.5 V

Vin1 (carrier) 8V pk-pk square wave at f<sub>c</sub> 10kHz.

Vin2 (modulation) 1.2V pk-pk sinewave at f<sub>m</sub> 1kHz to produce a.m. output with 100% modulation (see graph right) vout see waveforms opposite for 100% modulation.

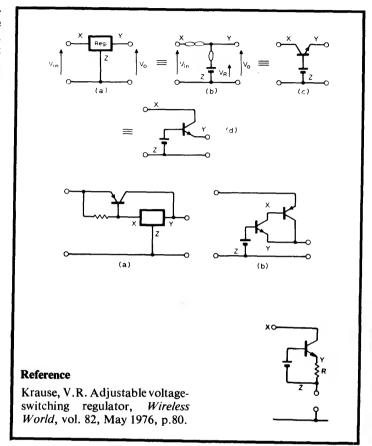

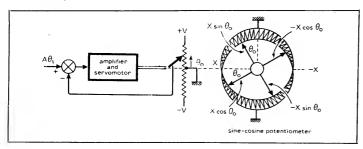

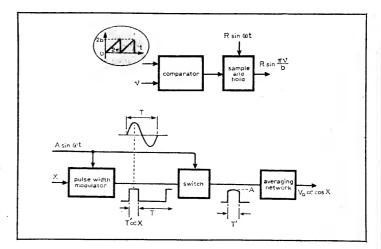

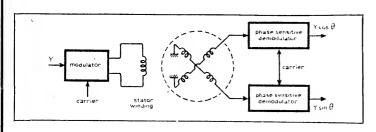

Circuit description