# **APPLICATION NOTE**

# DESIGNING WITH THE L4963 MONOLITHIC DISCONTINUOUS MODE POWER SWITCHING REGULATOR

by M Roncoroni

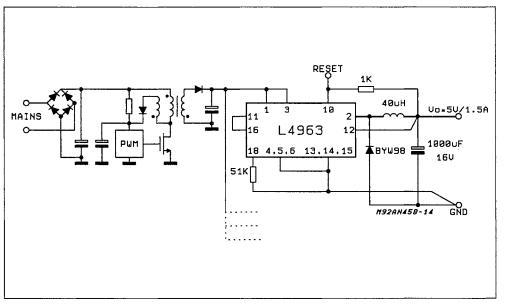

The L4963 is a new switching regulator designed to operate in discontinuous mode, reducing the number of the external components, giving a very cost effective solution. This application note explains how the device operates and how it can be used. Typical application circuits are also described.

The L4963 is a new monolithic stepdown switching regulator IC operating in discontinuous mode. This device, able to deliver 1.5A to the load at a voltage of 5.1V and up to 36V with derated current, is designed to satisfy very low cost applications due to the fact that the number of the external components are dramatically reduced.

Moreover the inductor value is reduced by a factor of three or four in comparison with a corresponding continuous mode solution. Also the plastic package (Powerdip 12+3+3), that needs no heatsink, contributes to decreasing the cost of the overall application.

Although the L4963 is intended for very low cost applications, it integrates features like remote in-

hibit, reset and power-fail outputs for microprocessor.

In the following we will explain in detail its principle of operation and the criteria that regulate the choice of the external components.

#### CIRCUIT OPERATION

The L4963 operates in discontinuous mode. In principle in this kind of operation the energy stored in the inductor is fully discharged to the load before to start a new cycle.

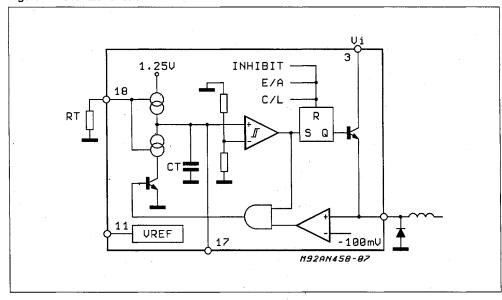

To operate in this way, the device contains, in its regulation loop, additional blocks compared to the usual Error/Amplifier, Oscillator and Pulse Width Modulator used in the continuous mode devices.

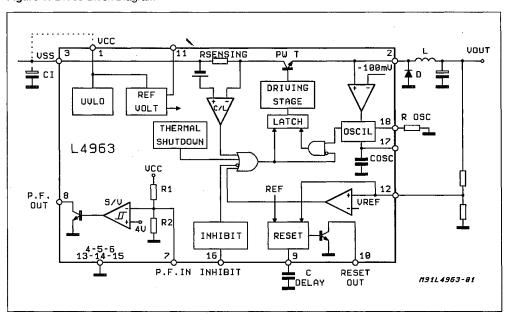

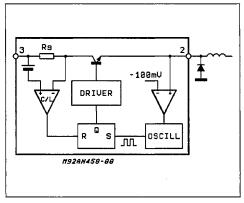

Figure 1: L4963 Block Diagram

Figure 2: Waveforms

The L4963 control loop is shown in the block diagram of fig.1 and the blocks that take part to the regulation loop, are determined by the system operating conditions.

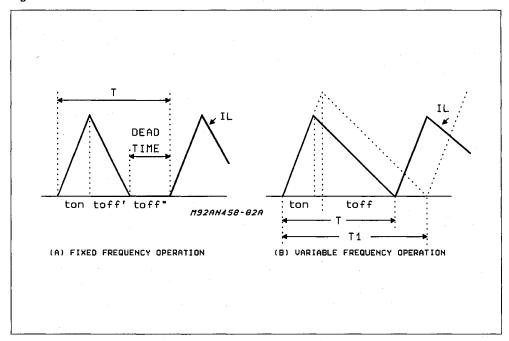

For a given value of the inductor L (that will be further calculated), if we examine the current across the inductor ( $I_{\rm L}$ ), we can have two different situations that modify the device operation. This two different conditions depend on the load current value that device has to deliver: changing the load current ( $I_{\rm O}$ ), the current through the inductor can have one of the shapes shown in fig. 2.

In both the waveforms, the current in the coil goes to zero during the Toff period of the power stage, but in the case shown in fig. 2A there is a "Dead Time" during which, both the Power stage and the Free-Wheeling diode are not conducting. The dead-time period ("Toff") increases lowering the load current. The system will start with a new cycle at the next set pulse coming from the clock. In this way the system operates in fixed frequency mode, set by the External resistor RT connected between pin. 17 and ground.

In fixed frequency mode, the current in the inductor reaches the peak value, determined by the load current, following the law:

$$I_{L+} = \frac{V_{in} - V_{cesat} - V_{out}}{L} \cdot t_{on} \quad (1)$$

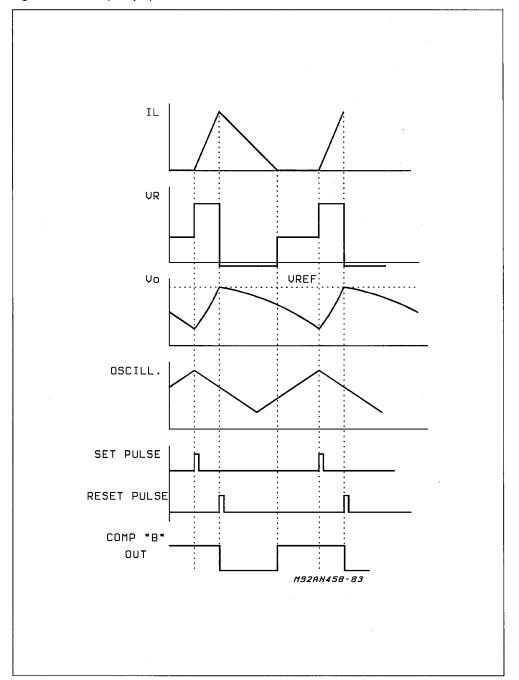

When the output voltage reaches its nominal value, the E/A output resets the power stage and the discharge period starts.

When the power transistor turns off, the inductor will try to mantain the forward current constant, and the voltage at pin.2 will fly negative until the diode D is brought into conduction. The current in the inductor L will now continue to circulate in the same direction as before, decreasing linearly from the peak value to zero following the law:

$$I_{L-} = I_{peak} - \frac{V_{out} + V_F}{L} \cdot t_{off} (2)$$

It follows, then, a third period toff" (dead time) during which there is no current neither across the power transistor, nor in the diode D, nor in the inductor L (the inductor runs 'DRY'). This period ceases when the next set pulse from the clock circuit enables again the power stage repeating the cycle.

The operation frequency is equal to the clock frequency, that is determined by the resistor  $R_t$ , connected between pin. 17 and ground:

$$f_{\text{osc}}\left(\text{KHz}\right) = \frac{0.033}{R_{t}\left(\text{K}\Omega\right)}$$

In fig.3 are shown the voltage and current waveforms associated to this mode of operation.

Figure 3: Fixed Frequency Operation

Referring again to the block diagram in fig. 1, and with a given inductor L, we suppose to have a load current that reduces the Dead Time toff" to zero. At this point we suppose that the clock send a set pulse to the latch and the power stage turns on. The current in the inductor grows from zero up to its peak value (Ipeak=2lout) following the law stated in Eq. 1.

If the peak current is below the Current Limitation threshold, it is again the Error Amplifier that turns off the power stage and the inductor will discharge following the eq. 2.

If the system is not able to discharge completely the inductor during the maximum toff time allowed by the fixed frequency operating mode an internal comparator, (which compares the voltage on the free-wheeling diode cathode with a precise internal reference Vr = -100mV) will mantain the power stage off until the inductor will be completely discharged.

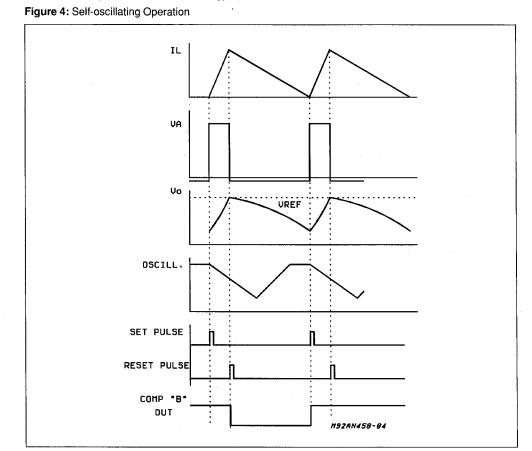

This comparator prevents the discharge of the internal timing capacitor C<sub>t</sub>, until the Energy in the inductor is completely discharged and the diode D ceases to conduct (see fig.4).

The system is working in a variable frequency mode, with a switching frequency that is depending on the current delivered to the load.

Bigger is the load current higher is the stored energy and longer is the time during which the comparator will block the discharge of the timing capacitor Ct, decreasing the system operating frequency. In fig.4 are shown the waveforms associated with this mode of operation.

## CALCULATION OF THE INDUCTANCE VALUE, L

To calculate the inductance, that is a critical element in the circuit, we have to consider that:

- The switching frequency increases reducing the load current l<sub>out</sub> and increasing V<sub>in</sub>.

- The switching frequency decreases increasing the load Current lout and decreasing Vin.

So to calculate the inductor value we have to

specify the minimum operation frequency (higher than 20KHz to avoid audible noise), for the minimum input voltage Vin at full load.

The equation to calculate the maximum inductor

$$L \leq \frac{(V_{in(min)}) \ - \ V_{cesat} \ - \ V_o) \ \cdot \ D}{2 \cdot \ I_{out(max)} \cdot \ f_{min}}$$

where: D =

$$\frac{V_o + V_F}{V_{in(min)} - V_{cesat} + V_F}$$

In overload or in short circuit conditions, the switching frequency decreases below the minimum limit fixed in standard operative conditions (f<sub>min</sub>). For this reason is important to select a f<sub>min</sub> with margin to avoid values inside the audible range in worst case.

Too low inductance values are not suitable because the increased ripple current in the core may generate too high ripple voltage in the output.

## Example:

We want to use the L4963 in an application in the following conditions:

$V_i = 15V$  to 35V

$V_0 = 5V$

$l_0 = 1.5A \text{ (max)}$

$f_{min} > 25KHz$

V<sub>cesat</sub>= 1.5V V<sub>F</sub> = **1**V

The right inductance for this application is calculated as follows:

$$D_{\text{max}} = \frac{5+1}{15-1.5+1} = 0.41$$

$$L \le \frac{(15 - 1.5 - 5) \cdot (0.41)}{2 \cdot 1.5 \cdot 25 \cdot 10^3} = 46 \mu H$$

Suggested value for L is in this case 40µH that corresponds to about a 15% less the max. allowed inductance.

#### **OUTPUT CAPACITOR SELECTION**

All the considerations for the choice of the filter capacitor in a system working in continuous mode are still valid in a discontinuous mode operation (Ref. L296 Appl.note). Let summarize the results with some useful suggestion for this specific sys-

The Ripple Voltage imposed on the D.C. output voltage is given by the sum of two terms. The first term (Vc), depends from ILpeak, Switch. Frequency and Cout values and the second (VESR) is due to Equivalent Series Resistance (ESR) of the capacitor multiplied by the ILpeak current.

$$V_o = V_c + V_{ESR}$$

(6)

Where:

$$V_c = \frac{I_{Lpeak}}{8 \cdot C_{out} \cdot f} = \frac{2I_{out}}{8 \cdot C_{out} \cdot f} = \frac{I_{out}}{4 \cdot C_{out} \cdot f}$$

(7)

$$V_{ESR} = I_{Lpeak} \cdot ESR = 2 \cdot I_{out} \cdot ESR$$

(8)

Once fixed the amount of ripple voltage desired for the application, with the first term we determine the minimum suitable capacitor value and with the second one we determine the maximum ESR acceptable.

Normally, for frequencies above 20KHz, the maximum ESR defines the choice of the filter capacitor value. In general, lower capacitor values have higher ESR ratings, so higher output capacitors than is calculated in eq. (7) should be used.

To guarantee a proper operation of the internal Error Amplifier, the minimum ripple voltage in the output must exceeds 15mV, to ensure a minimum voltage difference across its input terminals.

#### POWER DISSIPATION

It can be considered as the addition of three values:

$$Ptot = Psat + Pq + Psw$$

where:

Psat: Saturation losses of the power transistor plus the sensing resistor power dissipation.

Psat = V32 ·

$$I_0$$

·  $\frac{\text{ton}}{T}$  = V32 ·  $I_0$  ·  $\frac{V_0}{V_i}$

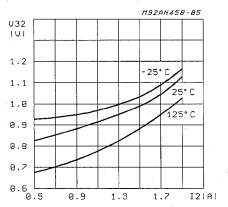

V32 = dropout voltage between input (pin 3) and output (pin 2).

For worst case (for I2 = 3A switch current) the V32 =

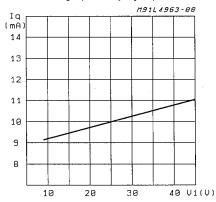

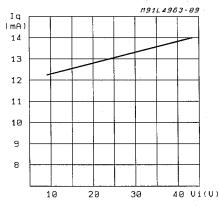

Pq: Losses due to the stand-by current and to the power driving current.

$$Pq = Vi \cdot I'3q + Vi \cdot I''3q = \frac{t_{on}}{T} = Vi \cdot I'3q + Vo \cdot I'' 3q$$

In fig. 6 and fig. 7 are showed these two typical values of guiescent current.

For the we worst case we can considered:

$$I"3q (100\% d.c.) = 17mA$$

Psw: Power transistor switching losses:

$$Psw = V_i \cdot I_O \cdot \frac{tr + tf}{2T}$$

Figure 5: V32 Voltage vs. Output Current

Figure 6: Quiescent Drain Current vs. Supply Voltage (0% Duty Cycle)

Figure 7: Quiescent Drain Current vs. Supply Voltage (100% Duty Cycle)

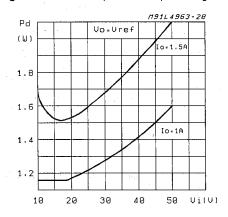

The fig. 8 shows the total power dissipation of the device.

For  $V_{out} > 5V$  the output current can be less then 1.5A. In fact we have to consider that the maximum power dissipation for this device is 2W at  $T_{amb}$  of  $70^{\circ}$  and is this value that limits the output current value.

Figure 8: Power Dissipation vs. Input Voltage.

## **EFFICIENCY**

The system efficiency is expressed by the following formula.

$$\eta\% = \frac{P_0}{P_i} \ 100$$

where Po = Vo Io (with Io = Iload)

is the output power to the load and  $P_i$  is the input power absorbed by the system.  $P_i$  is given by  $P_O$  plus all the other system losses. The expression of the efficiency becomes threfore the following.

$$\eta = \frac{P_O}{P_O + P_{sat} + P_q + P_{sw} + P_D + P_L}$$

The three terms concerning the device power losses have already been discussed in the previous paragraph.

We examine now the last two terms concerning the external components losses.

#### PD - Losses due to the recirculation diode

These losses increase as  $V_i$  increase, as in this case the ON time of the diode is greater.

$$PD = VF \cdot I_O \cdot \frac{V_i - V_O}{V_i} = VF \cdot I_O \cdot (1 - \frac{V_O}{V_i})$$

where VF is the forward voltage of the recirculation diode at current lo.

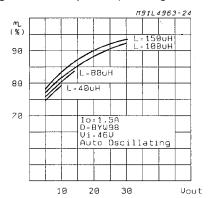

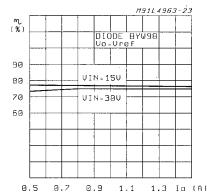

Figure 9: Efficiency vs. Output Voltage

Figure 10: Efficiency vs. Output Current

## PL - Losses due to the coil

Wecan divide these losses in two parts: core losses and copper losses.

The core losses for molypermalloy powder cores are given by the following formula.

Figure 11: Powerdip 12+3+3 Pin Connection

$$W = 0.568 \cdot f^{1.23} \cdot B^{2.56}$$

where W = watt/lb

f = KHz

$$B = KGauss = \frac{(V_i - V_O) \cdot V_O \cdot 10^8}{N \cdot Ae \cdot f \cdot V_i}$$

N = number of turns Ae = core cross section (cm<sup>2</sup>)

copper losses:

$$P - \rho I_0^2 MLT.N$$

N = number of turns

MLT = lenght/turn for 20% of winding factor  $\rho$  = copper resistivity (1.72 10E-6Wcm)

Refer to table 1 for some  $\rho$ /Aw suggest values.

Table 1

| AWG | Diameter<br>Copper<br>(cm) | OHMS/CM<br>20C | OHMS/CM<br>100C |

|-----|----------------------------|----------------|-----------------|

| 18  | .102                       | .000209        | .000280         |

| 19  | .091                       | .000264        | .000353         |

| 20  | .081                       | .000333        | .000445         |

| 21  | .072                       | .000420        | .000561         |

| 22  | .064                       | .000530        | .000708         |

Typical efficiencies obtained with the test and application circuit of fig. 20 are shown below.

## DEVICE DESCRIPTION

Fig.11 shows the pin connection of the Powerdip 12+3+3 plastic package. The internal block diagram of the device is shown in fig.1. Each block will now be examined in detail.

|   | SIGNAL SUPPLY VOLTAGE 1 18 R OSCILLATOR FREQ. |  |  |  |

|---|-----------------------------------------------|--|--|--|

| į | OUTPUT 🗖 2 17 🗖 C OSCILLATOR                  |  |  |  |

| į | SUPPLY VOLTAGE 🗖 3 16 🗖 INHIBIT INPUT         |  |  |  |

|   | GND 🗖 4 15 🖂 GND                              |  |  |  |

|   | GND 🗖 5 14 🖂 GND                              |  |  |  |

| į | GND 🗖 6 13 🗖 GND                              |  |  |  |

| 1 | P.FAIL INPUT 🗆 7 12 🗆 FEEDBACK INPUT          |  |  |  |

| i | P.FAIL OUTPUT   B   11   REFERENCE VOLTAGE    |  |  |  |

| į | RESET DELAY 🗖 9 10 🗖 RESET OUTPUT             |  |  |  |

|   | M91L 4963-02                                  |  |  |  |

| i |                                               |  |  |  |

#### POWER SUPPLY

The device has two separate pins dedicated for the supply source. Pin.1 is for the Signal (Vcc) and Pin.3 for the Power (Vss) source; normally these two pins are connected together (see the typical application circuit Fig. 18). The L4963 is provided with an internal stabilized power supply that feeds the precise internal voltage reference 5.1V (±2%) and the internal analog blocks.

## UNDER VOLTAGE LOCK OUT (UVLO)

The UVLO circuit ensures that Vcc is adequate to make the L4963 fully operational before enabling the output power stage. The UVLO turn-on and turn-off thresholds are internally fixed at 8.4V and 7.9V respectively.

This function acts also on the Power Fail and Reset Circuits; their output voltages pin.8 and pin.10 respectively, remain low state until the turn-on threshold is reached.

#### **OSCILLATOR**

The oscillator circuit behaves in a completely different way compared to the usual Step-Down regulator operating at fixed frequency and variable duty cycle. In fact, usually, the oscillator generates a fixed frequency sawtooth waveform that is compared with the Error Amplifier output voltage; generating the PWM signal to be sent to the power output stage.

In the L4963, the oscillator function is guite differ-

ent. In the following we will describe briefly its operation referring to the simplified internal schematic shown in fig.12.

It is composed of a comparator (with inputs compatible to ground) with an hysteresis whose thresholds are 1V and 4.1V respectively.

The oscillator uses an external resistor RT on pin.18 to establish the charging and discharging current of the internal timing capacitor CT = 50pF, fixing in this way the maximum switching frequency:

$f_{osc}(KHz) = \frac{0.033}{Rt (K\Omega)}$

It is also possible to increase the internal timing capacitor value, connecting an external capacitor between pin.17 and ground. The oscillator circuit, as we have seen in the "CIRCUIT OPERATION" paragraph, sends a set pulse to the latch that enables the power stage.

This set pulses train is at fixed frequency imposed by the external resistor when the device operates for low output currents (Dead time present in the inductor current I<sub>L</sub>).

When we are operating in self-oscillating mode, the comparator that senses the free-wheeling status disables the oscillator pulses output until the inductor is fully discharged, varying in this way the switching frequency. It is also possible to disable the oscillator forcing the system to operate always in self-oscillating mode, connecting-together the internal oscillator capacitor (pin.17) with the voltage reference pin.11.

Figure 12: Oscillator Circuit

#### CURRENT LIMITATION

Output overload protection is provided by a current limiter circuit. The load current is sensed by an internal metal resistor (Rs) in series to the power transistor. When the voltage drop on the sense resistor, reaches the current comparator offset voltage, the current comparator generates a reset pulse for the latch, disabling the power stage.

Typical current limiting threshold is around 4.5A. The power stage will be enabled again only when the energy stored in the inductor will be completely discharged, this due to the free-wheeling sense comparator (see Circuit operation paragraph for details).

The current limiting circuit operates also as softstart during the device turn-on preventing over-

currents on the load.

In fig.13 is shown the simplified internal schematic circuit of the current limiter.

Figure 13: Current Limiter

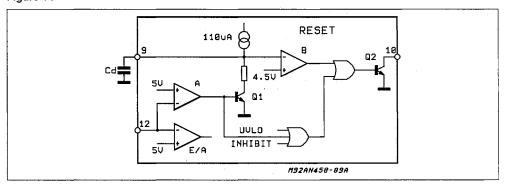

## Figure 14

#### RESET

The reset circuit accomplishes a very important function when the L4963 is used in applications where it feeds microprocessors and logic devices. The function block diagram is shown in Fig.14. The Reset circuit monitors the output voltage and generates a logic signal when the output voltage is within the limits required to supply correctly the microprocessor.

This function is realized through three pins:

- Feedback input (pin.12)

- Reset delay (pin.9)

- Reset output (pin.10)

When the monitored voltage on pin.12 is lower than 5V, the comparator (A) output is high and the reset delay capacitor is not charged because the transistor Q1 is saturated, also the transistor Q2 is saturated, mantaining the voltage on pin.10 at low level.

When the voltage on pin 12 exceeds 5V, the transistor Q1 switches off and the delay capacitor (Cd) starts to charge through an internal current generator of about 110µA. When the voltage on pin 9 reaches 4.5V, the output of the comparator (B) switches low and pin 10 goes high.

As the output is an open collector transistor (Q2), a pull-up external resistor is required.

On the contrary, when the Reset input voltage goes below 5V, with an hysteresis of 100mV, the comparator (A) triggers again and sets istantaneously the voltage on pin 10 low, therefore forcing to saturation the Q1 transistor, that starts the fast discharge of the delay capacitor.

As shown in the block diagram, the Reset output is low when the UVLO or The INHIBIT signals are present.

Inside the chip there is a digital filter that prevents the Reset circuit activation if V<sub>out</sub> drops below the reset threshold for less than 2s.

In this way the Reset circuit neglects very fast drops in the output voltage.

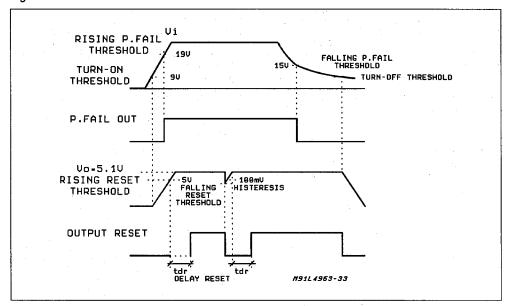

In fig.15 and Fig.16 are shown respectively the Reset circuit Waveforms and a typical application.

Figure 15

Figure 16

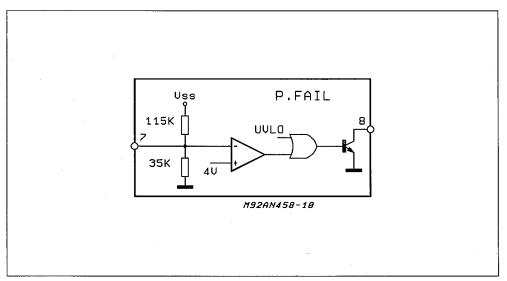

#### **POWER FAIL**

The Power-Fail circuit monitors the supply voltage (Vss) via an internal voltage divider (R1=115K $\Omega$ , R2=35K $\Omega$ ) as shown in Fig.17. When the supply voltage reaches the typical rising threshold voltage of 22V, set by the internal voltage divider, the Power Fail comparator output voltage goes low, turning off the output transistor Q1. This gives an high level on pin.8. As the power Fail output is an open collector transistor (Q1), an external pull-up resistor is required.

The Power Fail output goes low, giving an alarm signal, when the input voltage decreases reaching the internal typical Falling threshold voltage level of 18V. It is possible to change the rising and the falling threshold voltages, connecting a proper external voltage divider on pin.7. In fig. 15 are shown the power fail waveforms.

#### INHIBIT

The INHIBIT function, available on pin.16, disables the regulator with a TTL logic signal. An high level at this pin (above 2.2V) switches off the power stage and forces low the output reset. This useful feature, is normally used for supply sequencing and remote control ON-OFF.

#### THERMAL PROTECTION

The thermal protection function, operates when the junction temperature reaches 150°C; it acts directly on the power stage, turning it immediately off.

The thermal protection is provided with hysteresis and therefore, after an intervention has occurred, it is necessary to wait for the junction temperature to decrease of about 30°C below the intervention threshold.

#### APPLICATIONS

The L4963, thanks to the reduced external component count represents a very low cost effective solution in many applications.

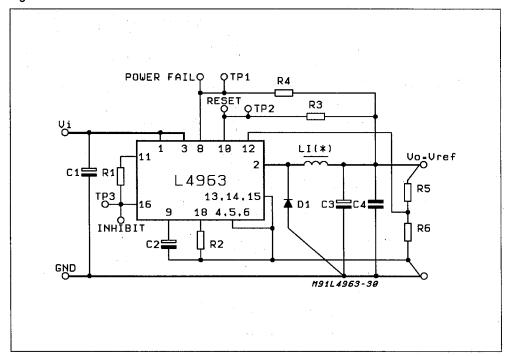

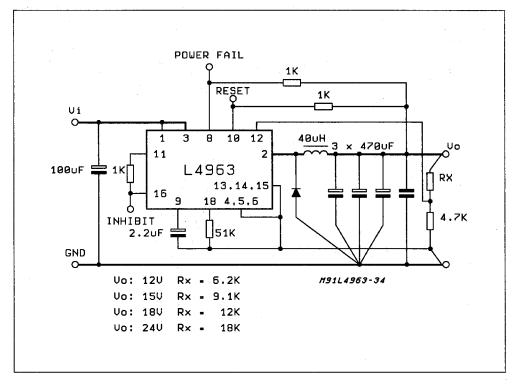

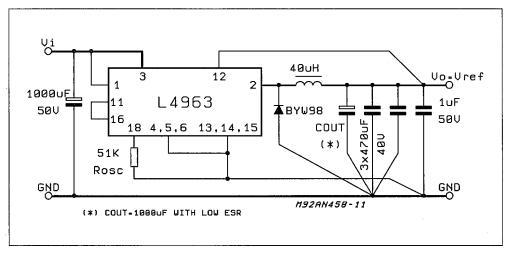

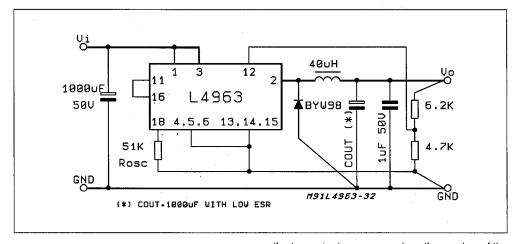

In Fig.18 the complete typical application circuit is shown, where all the functions available on the device are being used.

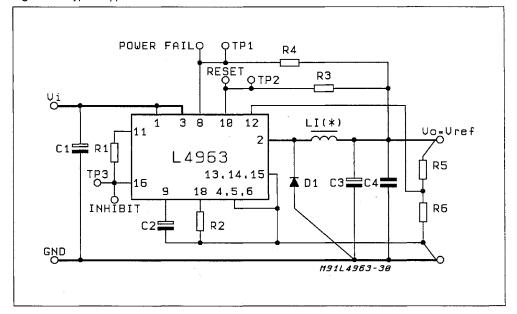

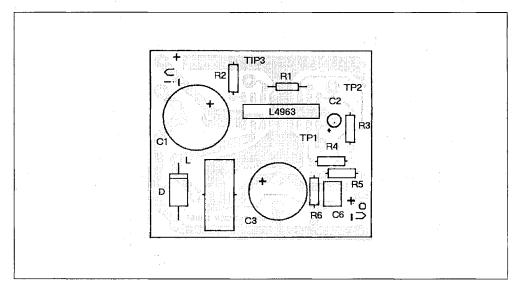

In fig.19 is shown the same application circuit for reduced filter capacitor count and its PCB. As evident the PCB dimensions are reduced.

Below we will describe the design procedure to follow and some suggestion regarding the external components to use.

Figure 17

Figure 18: Test and Application Circuit

## **PART LIST**

| CAPACITOR<br>DOµF 50V EKR (*) |  |  |

|-------------------------------|--|--|

| 00μF 50V EKR (*)              |  |  |

|                               |  |  |

| μ <b>F</b> 16V                |  |  |

| C3, C4, C5 4700μF 40V EKR     |  |  |

| = 50V film                    |  |  |

| RESISTOR                      |  |  |

| 1ΚΩ                           |  |  |

| 51ΚΩ                          |  |  |

| 1ΚΩ                           |  |  |

| 1ΚΩ                           |  |  |

| see table                     |  |  |

|                               |  |  |

| Resistor Value | Resistor Values for Standard Output Voltages |       |  |

|----------------|----------------------------------------------|-------|--|

| Vo             | R6                                           | R5    |  |

| 12             | 4.7ΚΩ                                        | 6.2ΚΩ |  |

| 15             | 4.7ΚΩ                                        | 9.1KW |  |

| 18             | 4.7ΚΩ                                        | 12KW  |  |

| 24             | 4.7ΚΩ                                        | 18KW  |  |

Diode: BYW98

Core: L = 40µH Magnetics 58121-A2MPP

34 Turns 0.9mm (20AWG)

(\*) Minimum  $100\mu F$  if  $V_i$  is a preregulated offline SMPS output or  $1000\mu F$  if a 50Hz transformer plus rectifiers is used.

Figure 29: Typical Application Circuit

## **PART LIST**

| CAPACITOR |                    |  |

|-----------|--------------------|--|

| C1        | 1000μF 50V EKR (*) |  |

| C2        | 2.2μF 16V          |  |

| C3        | 4700μF 40V EKR     |  |

| C4        | 1μF 50V film       |  |

| RESISTOR  |                    |  |

| R1        | 1ΚΩ                |  |

| R2        | 51ΚΩ               |  |

| R3        | 1ΚΩ                |  |

| R4        | 1ΚΩ                |  |

| R5, R6    | see table          |  |

| Resistor Value | Resistor Values for Standard Output Voltages |       |  |

|----------------|----------------------------------------------|-------|--|

| Vo             | R6                                           | R5    |  |

| 12             | 4.7ΚΩ                                        | 6.2ΚΩ |  |

| 15             | 4.7ΚΩ                                        | 9.1KW |  |

| 18             | 4.7ΚΩ                                        | 12KW  |  |

| 24             | 4.7ΚΩ                                        | 18KW  |  |

Diode: BYW98

Core: L = 40µH Magnetics 58121-A2MPP 34 Turns 0.9mm (20AWG)

(\*) Minimum 100μF if V<sub>i</sub> is a preregulated offline SMPS output or 1000μF if a 50Hz transformer plus rectifiers is used.

Figure 20: P.C. Board and Component Layout of the Circuit of fig. 21 (1:1 scale).

## L4963 Step-Down Regulator Design Example

Referring to the complete typical application circuit shown in fig.19, and defined the following conditions:

- V<sub>out</sub> = Regulated output voltage

- V<sub>in(min)</sub>= Minimum input voltage

- V<sub>in(max)</sub> = Maximum input voltage

- I<sub>out(max)</sub> = Maximum load current

- f<sub>min</sub> = Minimum switch freq. in self-oscillating mode.

We calculate the value of the external components.

## 1. OUTPUT VOLTAGE SETTING:

The output voltage is established by the voltage divider constituted by R5 and R6. To select the right R5 value use the following formula:

$$R5 = \frac{(V_{out} - V_{ref})}{V_{ref}} (R6)$$

where:  $V_{ref} = 5.1V$

R6 = is normally set at  $4K7\Omega$

For a Quick calculation of some standard output voltages, the following table is useful:

| Resistor Value       | Resistor Values for Standard Output Voltages |                                |  |

|----------------------|----------------------------------------------|--------------------------------|--|

| Vo                   | R6                                           | R5                             |  |

| 12<br>15<br>18<br>24 | 4.7KΩ<br>4.7KΩ<br>4.7KΩ<br>4.7KΩ             | 6.2KW<br>9.1KΩ<br>12KΩ<br>18KΩ |  |

To obtain  $V_{\text{out}} = V_{\text{ref}}$ , the pin.12 is directly connected to the output, therefore eliminating both R5 and R6.

#### 2. INDUCTOR SELECTION:

The max. duty cycle is determined by the following formula:

$$D_{max} = \frac{V_{out} + V_F}{V_{in(min)} - V_{ce(sat)} + V_F}$$

Where:  $V_{ce(sat)} = 1.5 \text{ V}^{-}$  $V_F = \text{Catch diode forward drop}$

The maximum inductor value is then calculated:

$$L max = \frac{(V_{in(min)} - V_{ce(sat)} - V_{out})}{2 \cdot I_{out(max)} \cdot f(min)} \cdot D max$$

where:

f(min) 20KHz to be out of the audible range.

In discontinuous mode operation, the inductor current may reach very high peaks ( $I_{Peak} = 2I_{out}$ ), so it is important to verify that the coil will not saturate in overload or short circuit conditions damaging the output power stage due to the high dl/dt ratio.

Therefore, a correct dimensioning requires a saturation current above the maximum current limit threshold ( $I_{2max-peak} = 6A$ ).

## 3. Output Capacitor Selection:

The output voltage ripple depends on the current ripple in the inductor and on the performance of the output capacitor at the switching frequency. The minimum value of the output filter capacitor is obtained from:

$$C_{out(min)} \, = \, \frac{I_{out(max)}}{4 \cdot V_{ripple(p\!-\!p)} \cdot fmin}$$

where  $V_{ripple(p-p)}$  is the amount of ripple voltage desired.

Clearly this formula doesn't take care of the capacitor Equivalent Series Resistance (ESR) value, that is the dominant factor to define the output ripple voltage at switching frequencies greater than 20KHz.

So we suggest to use also the following formula:

$$ESR(max) = \frac{V_{ripple(p-p)}}{2 \cdot I_{out(max)}}$$

Where the ESR(max) requirement is not satisfied by the capacitor value given by the first formula, use an higher value or, better, put in parallel several capacitors in order to reduce the total ESR. The capacitors' voltage rating should be at least 1.25 times greater than the given output voltage.

The big advantage of this system is to greatly reduce number of external components compared to the continuous mode solution.

The only drawback is a higher ripple voltage on the output that can be up three times larger than in continuous mode.

A proper choice of low ESR filtering capacitors

can solve this problem greatly reducing the output ripple.

#### 4. CATCH DIODE SELECTION:

The catch diode must comply with several requirements and its choice requires special care. The current rating must be at least 1.2 times greater respect the maximum load current, but

greater respect the maximum load current, but this is not enough because in short circuit conditions, the maximum current limiter threshold is 6A to which correspond an average output current of  $l_{out} = l_{peak/2} = 3A$ . This is the current requirement to use to choose the right diode.

The reverse voltage rating of the diode should be at least 1.25 times the maximum input voltage.

The diode recovery speed is not so important because the power stage is turned-on only when the inductor is fully discharged and the diode is definitely off. So there is not simultaneous conduction between them.

This allows a reduction of the disturbances with respect to the continuous mode, because they are mainly radiated during the transistor switch on, for the steep slopes during the simultaneous conduction of transistor and reverse conduction-diode.

## LOW COST APPLICATION

If the remote inhibit, the reset and the power fail functions are not used we can reduce further the external component count.

It is possible in this case, to have a very efficientswitch mode power supply for very low cost applications.

Two examples of minimal component count regulators are shown in fig.21 and fig.22.

Figure 21: A Minimal 5.1 Fixed Regulator – Very Few Components are Required

Figure 22: A Minimal Components count for Vo = 12V

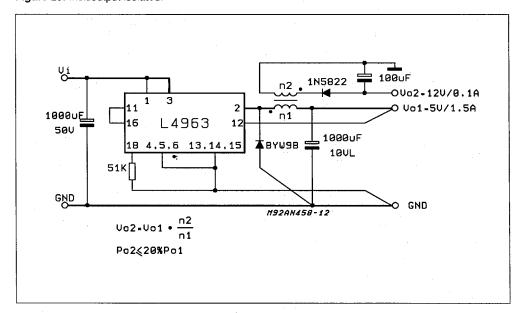

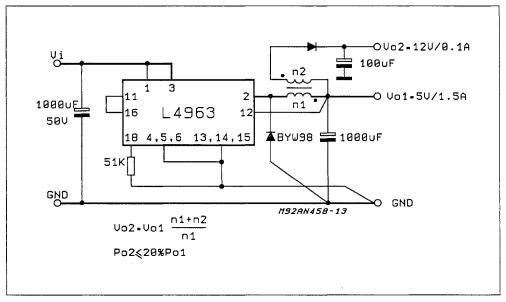

#### **DUAL OUTPUT POWER SUPPLY**

The application shown in fig.23 is interesting because it provides two output voltages. The main voltage, is directly controlled by the feedback loop, the second voltage is obtained through an auxiliary winding. As the auxiliary voltage is obtained through a completely separated winding, it is possible to obtain either a positive or a negative voltage. Where isolation is not required between

the two outputs, we can reduce the number of the auxiliary turns improving also the tolerance of the secondary output using the configuration illustrated in fig.24.

For both this configurations, the discontinuous mode is ideal because we have a good energy transfer between primary and secondary windinngs, due to the high energy stored in the coil that is function of the ripple current in the inductor.

Figure 23: Multioutput isolated.

Figure 24: Multioutput not isolated.

## L4963 IN OFF-LINE POWER SUPPLY

The L4963 can be useful as post regulator in offline power supplies, where it can sobstitute the usual linear post regulation increasing the efficiency and reducing the complexity of the transformer, if the distributed power supply approach is used (see fig.25).

Figure 25: Typical off-line solution using L4963 as post regulator.