# **Analog Applications Journal**

# **DESIGN BRIEF**

# Understanding Output Voltage Limitations of DC/DC Buck Converters

#### By John Tucker Applications Engineer

Applications Engine

# Introduction

Product datasheets for DC/DC converters typically show an operating range for input and output voltages. These operating ranges may be broad and in some cases may overlap. It is usually not possible to derive any arbitrary output voltage from the entire range of permissible input voltages. There are several factors that can cause this, including the internal reference voltage, the minimum controllable ON time, and the maximum duty-cycle constraints.

# **Ideal Buck-Converter Operation**

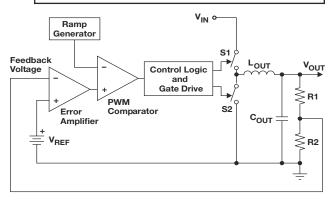

Consider the theoretical, ideal buck converter shown in Figure 1. The buck converter is used to generate a lower output voltage from a higher DC input voltage.

If the losses in the switch and catch diode are ignored, then the duty cycle, or the ratio of ON time to the total period, of the converter can be expressed as

$$D = \frac{V_{OUT}}{V_{IN}}.$$

(1)

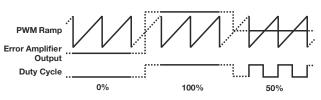

The duty cycle is determined by the output of the error amplifier and the PWM ramp voltage as shown in Figure 2. The ON time starts on the falling edge of the PWM ramp voltage and stops when the ramp voltage equals the output voltage of the error amplifier. The output of the error amplifier in turn is set so that the feedback portion of the output voltage is equal to the internal reference voltage. This

closed-loop feedback system causes the output voltage to regulate at the desired level. If the output of the error amplifier falls below the PWM ramp minimum, then a 0% duty cycle is commanded,

## Featured in the latest online issue

- Understanding the pen-interrupt operation of touch-screen controllers

- Understanding output voltage limitations of DC/DC buck converters

- Battery-charger front-end IC improves charging-system safety

- Using the CC2430 and TIMAC with low-power wireless sensors: A power-consumption study

- Selecting antennas for low-power wireless applications

- Download your copy now at www.ti.com/aaj

Figure 1. Theoretical, ideal buck converter.

Figure 2. Typical PWM waveforms.

the converter will not switch, and the output voltage is 0 V. If the error-amplifier output is above the PWM ramp peak, then the commanded duty cycle is 100% and the output voltage is equal to the input

voltage. For error-amplifier outputs between these two extremes, the output voltage will regulate to

$$V_{OUT} = D \times V_{IN}.$$

(2)

#### **Practical Limitations**

For the ideal buck converter, any output voltage from 0 V to VIN may be obtained. In actual DC/DC converter circuits, there are practical limitations. It has been shown that the output voltage is proportional to the duty cycle and input voltage. Given a particular input voltage, there are limitations that prevent the duty cycle from covering the entire range from 0 to 100%. Most obvious is the internal reference voltage, V<sub>BEE</sub> Normally, a resistor divider network as shown in Figure 1 is used to feed back a portion of the output voltage to the inverting terminal of the error amplifier. This voltage is compared to V<sub>REF</sub>; and, during steady-state regulation, the error-amplifier output will not go below the voltage required to maintain the feedback voltage equal to V<sub>REF</sub>. So the output voltage will be

$$V_{OUT} = V_{REF} \left( \frac{R1}{R2} + 1 \right).$$

(3)

As R2 approaches infinity, the output voltage goes to  $V_{\text{REF}}$  so that the output cannot be regulated to below the reference voltage.

There may also be constraints on the minimum controllable ON time. This may be caused by limitations in the gate-drive circuitry or by intentional delays. This minimum controllable ON time puts an additional constraint on the minimum achievable V<sub>OUT</sub>:

$$V_{OUT(min)} = t_{on(min)} \times V_{IN} \times f_{s}, \qquad (4)$$

where  $t_{on(min)}$  is the minimum controllable ON time and  $f_s$  is the switching frequency.

The duty cycle may also be constrained at the upper end. In many converters, a dead time is required to charge the high-side switching FET gatedrive circuit. Feedforward circuitry may also cause a flattening of the PWM ramp waveform as the slope of the PWM ramp is increased while the period remains constant. This will limit the maximum output voltage with respect to  $V_{IN}$ . Typically, if there is a maximum duty-cycle limit, it will be expressed as a percentage, and the maximum output voltage will be

$$V_{OUT(max)} = V_{IN} \times D_{max}.$$

(5)

#### **Effect of Circuit Losses**

So far we have assumed that the components in the circuit are ideal and lossless. Of course, this is not the case. There are conduction losses associated with the components that are important in determining the minimum and maximum achievable output voltage. Most important of these are the ON resistance of the high- and low-side switch elements, and the series resistance of the output inductor. Taking these losses into account, we can now express the duty cycle of the converter as

$$D = \frac{V_{OUT} + I_{OUT} \times (r_{DS2} + R_L)}{V_{IN} - I_{OUT} \times (r_{DS1} - r_{DS2})},$$

(6)

where  $r_{DS1}$  is the ON resistance of the high-side switch, S1;  $r_{DS2}$  is the ON resistance of the low-side switch, S2; and  $R_L$  is the output-inductor series resistance. Since the loss terms are added to the numerator and subtracted from the denominator, the duty cycle increases with increasing load current relative to the ideal duty cycle. This has the effect of increasing the available minimum voltage. The worstcase situation for determining the minimum available output voltage occurs when the input voltage is at its maximum specification, the output current is at the minimum load specification, and the switching frequency is at its maximum value. The minimum output voltage is then

$$V_{OUT(min)} = t_{on(min)} \times f_{s(max)} \times [V_{IN(max)} - I_{OUT(min)} (7) \times (r_{DS1} - r_{DS2})] - [I_{OUT(min)} \times (r_{DS2} + R_L)].$$

In contrast, the loss terms decrease the available maximum voltage, and the worst-case conditions occur at the minimum input voltage and maximum load current. Since the limiting factor, maximum duty cycle, is specified as a percentage, the switching frequency is not relevant. The maximum available output voltage is given by

$$V_{\text{OUT}(\text{max})} = D_{\text{max}} \times [V_{\text{IN}(\text{min})} - I_{\text{OUT}(\text{max})} \times (r_{\text{DS1}} - r_{\text{DS2}})] - [I_{\text{OUT}(\text{max})} \times (r_{\text{DS2}} + \text{R}_{\text{L}})].$$

(8)

Please see Reference 1 for the complete version of this article, which includes typical application examples with calculated minimum and maximum output voltages.

#### Conclusion

While the ideal buck converter can theoretically provide any output voltage from  $V_{IN}$  down to 0 V, practical limitations do exist. The output voltage cannot go below the internal reference voltage, and internal circuit operation may limit the minimum ON time and maximum duty cycle. Additionally, real-world circuits contain losses. These losses can act to extend the duty cycle at higher load currents and may be an advantage when output-voltage extremes exist.

### Reference

1. View the complete article at http://www-s.ti.com/sc/techlit/slyt293