# Designing instrumentation circuitry with rms/dc converters

### RMS CONVERTERS RECTIFY AVERAGE RESULTS.

sing rms to measure waveforms furnishes the most accurate amplitude information (Reference 1). Rectify-and-average schemes, which you usually calibrate to a sine wave, are accurate for only one waveshape, however. Departures from this waveshape result in pronounced errors. Although accurate, rms conversion often entails limited bandwidth, restricted range, complexity, and difficult-to-characterize dynamic and static errors. Recent developments address these issues and also improve accuracy. Table 1 at the Web version of this article at www.edn.com/ms4228 shows Linear Technology's (www.linear.com) LTC1966/LTC1967/LTC1968 device family. The devices feature low-frequency accuracy, including linearity and gain error, of 0.5% and 1% error at bandwidths extending to 500 kHz. These converters employ a sigma-delta-based computational scheme to achieve their perfor-

Figure 1's pinout descriptions and basic circuits reveal an easily applied device. An output filter capacitor is all that is necessary to form a functional rms/dc converter. The figure shows split- and single-supply-powered variants. Such ease of

implementation invites a broad range of application; examples begin with Figure 2.

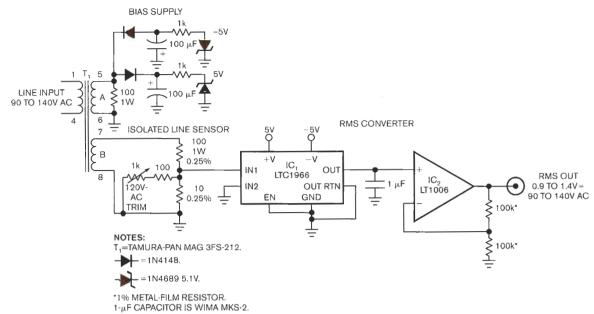

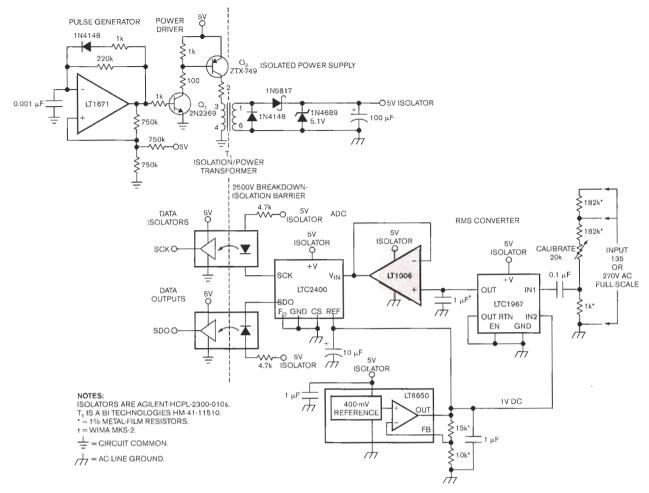

# ISOLATED POWER-LINE MONITOR

Figure 2's ac-power-line monitor has 0.5% accuracy over a sensed 90 to 130V-ac input and provides a safe, fully isolated output. Conversion of rms provides accurate reporting of ac-line voltage, regardless of waveform distortion, which is common. T<sub>1</sub>'s ratio divides down the ac-line voltage. An isolated and reduced potential appears across T,'s secondary, B, at which it resistively scales and presents itself to IC,'s input. Power for IC, comes from T,'s secondary, A, which you rectify, filter, and zener-regulate to dc. IC, provides a numerically convenient output from gain. You can increase accuracy by biasing T, to an optimal loading point, which the relatively low-resistance-divider values facilitate. Similarly, although IC, and IC, can operate from one supply, split supplies maintain symmetrical T, loading. You calibrate the circuit by adjusting the 1-k $\Omega$  trim for 1.20V output with the ac line at 120V ac. You make this adjustment using a variable-ac-line transformer and a floating rms voltmeter (see sidebar "AC-measurement

and signal-handling practice" at the Web version of this article at www.edn.com/ms4228 for recommendations on rms voltmeters and other ac-measurementrelated gossip).

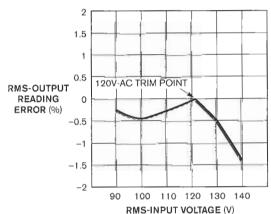

Figure 3's error plot shows 0.5% accuracy from 90 to 130V ac, degrading to 1.4% at 140V ac. The beneficial effect of trimming at 120V ac is evident; trimming at full-scale would result in larger overall error, primarily due to nonideal-transformer behavior. Note that the data is specific to the transformer. Substitution for T<sub>1</sub> necessitates circuit-value changes and recharacterization.

#### 2.7 TO 5.5V DEPENDING ON DEVICE CHOICE OUTPUT TO FILTER DIFFERENTIAL O CAPACITOR OOUTPUT INPUT 1 OUTPUT INPUTS LTC1966 MAXIMUM COMMON-MODE LTC1967 RANGE - ± V SUPPLY LTC1968 OUTPUT REFERRED MAXIMUM DIFFERENTIAL= 1V. OUTPUT RETURN INPUT 2 O TO THIS PIN. MINIMUM INPUT=5 mV NORMALLY GROUNDED ENABLE GND SET HIGH LTC1966 ONLY POWER \*NO -V PIN ON THE LTC1967/LTC1968. TO 0 TO -5V GROUND SHUT DOWN SUPPLY 5\ 0 5V Q V<sub>DD</sub> $V_{DD}$ DC+AC INPUTS DC OUTPUT DC OUTPUT VON 0 AC INPUTS O 0 $Z_0 = 85 \text{ k}\Omega.$ $Z_0=85 \text{ k}\Omega$ Lcavg LTC1966 LTC1966 (1V PEAK (1V PEAK IN2 OUT RTN DIFFERENTIAL) N2 OUT RTN V<sub>SS</sub> GND EN S GND EN

POSITIVE SUPPLY

Figure 1 The pinout descriptions (top) and basic circuits (bottom) include the rms converter's pin functions and application circuits. The pins' descriptions are equivalent in all the devices, with only minor differences.

# **FULLY ISOLATED**

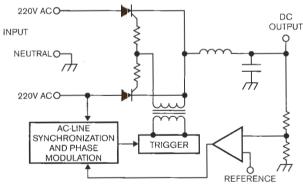

RMS/dc converters commonly require accurate rms-amplitude measurement of an SCR's (silicon-controlled rectifier's) chopped ac-line waveforms. The

Figure 2 This isolated power-line monitor senses with a transformer and provides 0.5% accuracy from 90 to 130V-ac input. Loading the transformer secondary optimizes the voltage conversion's linearity.

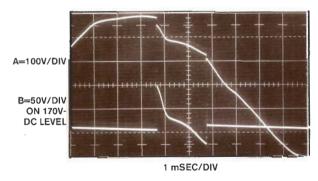

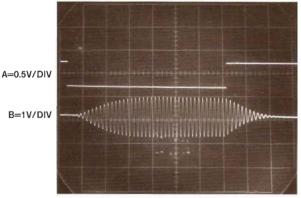

SCR's fast sine-wave switching complicates this measurement because this speed introduces odd waveshapes with high-frequency harmonic content. Figure 4's conceptual SCR-based ac/dc converter is typical. The SCRs alternatively chop the 220V-ac line, responding to a loop-enforced, phase-modulated trigger to maintain a dc output. Figure 5's waveforms show typical operation. Trace A represents one ac-line phase, and Trace B represents the SCR cathodes. The SCR's irregularly shaped waveform contains dc and high-frequency harmonics, requiring wideband rms conversion for measurement. Additionally, for safety and system-interface considerations, you must fully isolate the measurement.

**Figure 6** provides isolated power and data-output paths to an rms/dc converter, permitting safe, wideband, digital output-rms

Figure 3 The line monitor has 0.5% accuracy from 90 to 130V ac, degrading to 1.4% accuracy at 140V ac. Almost all the error is due to transformer parasitic losses.

Figure 4 This ac/dc converter is typical of SCR-based designs. Feedback directs the SCR, which synchronizes with the ac line. The SCR's trigger-phase modulation controls the dc output.

Figure 5 Trace A is the ac line of the SCR-based ac/dc converter. Trace B is the waveform at the SCR cathode. It contains dc and high-frequency harmonics that require wideband rms measurement to ensure accurate regulation.

Figure 6 Optoisolators provide a safe, low-voltage digital output for this wideband-rms-measurement circuit. T<sub>1</sub> and associated circuitry provide isolated power for the rms converter, and a resistive divider performs high-voltage ac sensing. An ADC provides a serial output to the optoisolators. The accuracy of this circuit is 1% over a 200-kHz bandwidth.

measurement. A pulse-generator-configured comparator combines with  $Q_1$  and  $Q_2$  to drive  $T_1$ , resulting in isolated 5V power at  $T_1$ 's rectified, filtered, and zener-regulated output. The rms/dc converter senses either 135 or 270V-ac full-scale inputs through a resistive divider. The converter's dc output feeds a self-clocked, serially interfaced ADC; optocouplers convey output data across the isolation barrier. The LTC6650 provides a 1V reference to the ADC and biases the rms/dc converter's inputs to accommodate the voltage divider's ac swing. You accomplish calibration by adjusting the  $20\text{-k}\Omega$  trim and noting that output data agrees with the input ac voltage. Circuit accuracy is within 1% in a 200-kHz bandwidth.

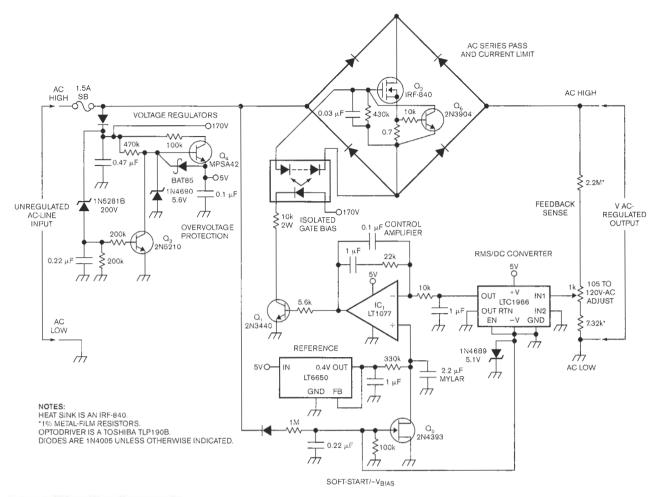

# LOW-DISTORTION AC-LINE RMS REGULATOR

Almost all functioning ac-line-voltage regulators rely on some form of waveform chopping, clipping, or interruption. This requirement promotes efficiency but introduces waveform distortion, which is unacceptable in some applications. Figure 7 regulates the ac line's rms value within 0.25% over wide input swings and introduces no distortion. It accomplishes this task by continuously controlling the conductivity of a seriespass MOSFET in the ac line's path. Enclosing the MOSFET

in a diode bridge permits it to operate during both ac-line po-

You apply the ac-line voltage to the Q<sub>3</sub>-diode bridge. A calibrated variable-voltage divider senses this bridge and feeds IC,. You route IC,'s output, representing the regulated line's rms value, to control amplifier IC, and compare it with a reference. IC,'s output biases Q1, controlling drive to a photovoltaic optoisolator. The optoisolator's output voltage provides level-shifted bias to diode-bridge-enclosed Q,, closing a control loop, which regulates the output's rms voltage against ac-line and -load shifts. RC components in IC,'s local feedback path stabilize the control loop. The loop operates Q, in its linear region, much like a common low-voltage dc linear regulator. The result is the absence of introduced distortion at the expense of lost power. Heat dissipation constrains the available output power. For example, when you set the output adjustment to regulate 10V below the normal input, Q, dissipates about 10W at 100W output. You can improve this figure, however. The circuit regulates for  $V_{IN}{\ge}2V$  above  $V_{OUT}$  but operation in this region risks regulation dropout as  $V_{IN}$  varies.

Circuit details include JFET  $Q_5$  and associated components. The passive components associated with  $Q_5$ 's gate form a slow

Figure 7 This ac-line-voltage regulator introduces no waveform distortion.  $IC_2$  senses the rms value of line voltage and compares it with a reference.  $IC_2$  then biases the photovoltaic optocoupler through  $O_1$ ,  $O_2$  sets the diode bridge's conductivity and closes the control loop. The input voltage must be 2V higher than the output voltage to maintain regulation.

turn-on negative supply for IC<sub>1</sub>. They also provide gate bias for  $Q_5$ , a soft-start transistor that prevents abrupt ac power application to the output at start-up. When power is off,  $Q_5$  conducts, holding IC<sub>2</sub>'s positive input low. When you apply power, IC<sub>1</sub> initially has a 0V reference, causing the control loop to set the output at zero. As the 1 MΩ, 0.22-μF combination charges,  $Q_5$ 's gate moves negative, causing its channel conductivity to gradually decay.  $Q_5$  ramps off, IC<sub>2</sub>'s positive input moves smoothly toward the LT6650's 400-mV reference, and the ac output similarly ascends toward its regulation point. Current sensor  $Q_6$ , measuring across the 0.7Ω shunt, limits output current to approximately 1A. At normal line inputs of 90 to 135V ac,  $Q_4$  supplies 5V operating bias to the circuit. If line voltage rises beyond this point,  $Q_3$  comes on, turning off  $Q_4$  and shutting down the circuit.

# **GAIN-OF-1000 PREAMPLIFIERS**

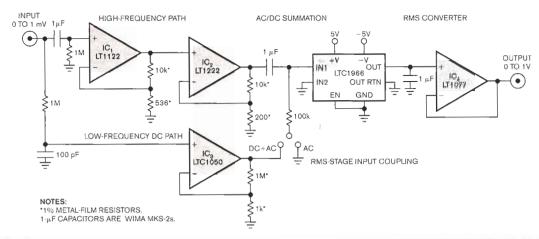

The preceding circuits furnish high-level inputs to the rms converter. Many applications lack this advantage and require some form of preamplifier. High gain preamplification for the rms converter requires more attention than you might suppose. The preamplifier must have low offset error because the rms converter (desirably) processes do as legitimate input. More

subtly, the preamplifier must have far more bandwidth than is immediately apparent. The amplifier's -3-dB bandwidth is of interest, but its closed-loop 1%-amplitude-error bandwidth must be high enough to maintain accuracy over the rms converter's 1%-error passband. This requirement is not trivial, because very high open-loop gain at the maximum frequency of interest is necessary to avoid inaccurate closed-loop gain.

Figure 8 shows a gain-of-1000 preamplifier that preserves the LTC1966's dc to 6-kHz, 1% accuracy. The amplifier may be either ac- or dc-coupled to the rms converter. The 1-mV full-scale input splits into high- and low-frequency paths. IC<sub>1</sub> and IC<sub>2</sub>, which are both ac-coupled, take a cascaded, high-frequency gain of 1000. Chopper-stabilized IC<sub>3</sub> which is dc-coupled, also has a gain of 1000, but its RC-input filter restricts it to operate only at dc and low-frequency. Assuming the switch is set to dc+ac, high- and low-frequency-path information recombine at the rms converter. The high-frequency path's 650-kHz, -3-dB response combines with the low-frequency section's microvolt-level offset to preserve the rms converter's dc to 6-kHz 1% error. If you require only ac response, set the switch to the appropriate position. The minimum processable input, which the circuit's noise floor sets, is 15 μV.

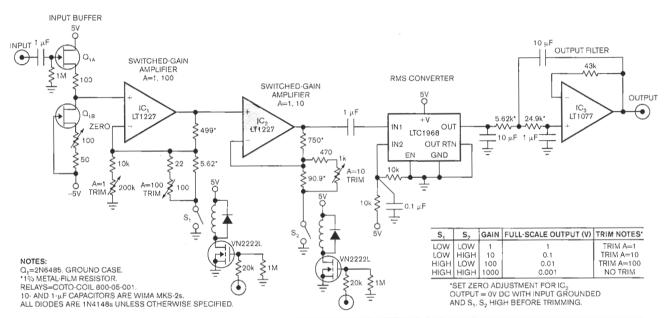

The LTC1968, with a 500-kHz, 1%-error bandwidth, poses a

Figure 8 This gain-of-1000 preamplifier allows rms-to-dc conversion with 1-mV full-scale sensitivity. The input splits into high- and low-frequency paths that recombine at the rms converter. The amplifier's 650-kHz, -3-dB bandwidth preserves the rms converter's 6-kHz, 1%-error bandwidth. The noise floor of this circuit is 15 μV.

Figure 9 This switched-gain, 10-MHz, ~3-dB ac preamplifier preserves the LTC1968's 500-kHz, 1%-error bandwidth. The decade ranged gains allow a 1-mV full-scale reading with a 20-μV noise floor. The JFET-input stage provides high input impedance. AC coupling and a third-order Sallen-Key filter maintain 1% accuracy down to 10 Hz.

significant challenge for an accurate preamplifier, but the circuit in **Figure 9** meets the requirement. This design features decade-ranged gain to 1000 with a 1%-error bandwidth beyond 500 kHz, preserving the rms converter's 1%-error bandwidth. Its 20- $\mu$ V noise floor maintains wideband performance at microvolt-level inputs.  $Q_{1A}$  and  $Q_{1B}$  form a low-noise buffer, permitting high-impedance inputs. IC<sub>1</sub> and IC<sub>2</sub>, which are both gain-switchable, take cascaded gain in accordance with the **figure**'s table. You set the gains using reed relays, which a 2-bit code controls. IC<sub>2</sub>'s output feeds the rms converter, and a Sallen-Key active filter smoothes the converter's output. The circuit maintains 1% error over a 10-Hz to 500-kHz bandwidth at all gains due to the preamplifier's -3-dB, 10-MHz bandwidth. You can eliminate the 10-Hz, low-frequency restriction

with a dc-stabilization path similar to the one in Figure 8, but you would have to switch its gain in concert with the  $\rm IC_1$ - $\rm IC_2$  path.

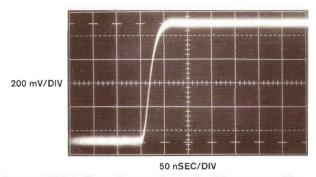

Figure 10 shows preamplifier response to a 1-mV input step at a gain of 1000. IC2's output is singularly clean, with trace thickening in the pulse's flat portions due to the 20- $\mu$ V noise floor. The 35-nsec rise time indicates a 10-MHz bandwidth. To calibrate this circuit, first set  $S_1$  and  $S_2$  high, ground the input, and trim the zero adjustment for 0V dc at IC2's output. Next, set  $S_1$  and  $S_2$  low, apply a 1V, 100-kHz input, and trim A=1 for unity gain, which you measure at the circuit output, in accordance with the table in **Figure 9**. Continue this procedure for the remaining three gains in the table. A good way of generating the required accurate low-level inputs is to set a 1V-ac lev-

el and divide it down with a high-grade  $50\Omega$  attenuator, such as the Hewlett-Packard (www.hp.com) 350D or the Tektronix (www.tektronix.com) 2701. It is prudent to verify the attenuator's output with a precision rms voltmeter (see sidebar "ACmeasurement and signal-handling practice" at the Web version of this article at www.edn.com/ms4228).

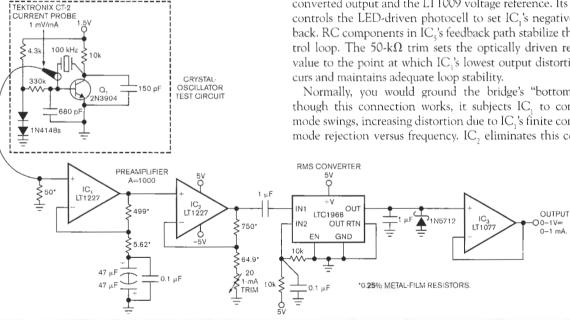

#### MEASURING QUARTZ-CRYSTAL RMS CURRENT

Quartz-crystal rms operating current is critical to long-term stability, temperature coefficient, and reliability. You must minimize introduced parasitics, particularly capacitance, which corrupt crystal operation. This requirement complicates accurate determination of rms-crystal current. Figure 11, a form of Figure 9's wideband amplifier, combines with a commercially available closed-core current probe to permit the measurement. An rms/dc converter supplies the rms value. The quartz-crystal test circuit in dashed lines exemplifies a typical measurement situation. The Tektronix CT-2 current probe monitors crystal current and introduces minimal parasitic loading. The probe's  $50\Omega$  termination allows direct connection to IC, without the FET buffer in Figure 9. Additionally, because quartz crystals are uncommon at frequencies lower than 4 kHz, IC,'s gain does not extend to low frequency.

Figure 12 shows the results. A crystal drive, which you take at  $Q_1$ 's collector (Trace A), causes a 25- $\mu$ A-rms crystal current, which appears at the rms/dc-converter input (Trace B). The trace enlargement is due to the preamplifier's 5-µA-rms equivalent-noise contribution. Table 2 at the Web version of this article at www.edn.com/ms4228 details characteristics of two Tektronix closed-core current probes. The primary trade-off is low-frequency error versus sensitivity. The current probes contribute essentially no probe noise, and capacitive loading is notably low. You calibrate the circuit by putting 1-mA rms cur-

Figure 11 The circuit of Figure 9 adapts to the isolated true-rms measurement of the current in a quartz crystal. The current probe's 500 impedance allows the elimination of the FET-input buffer and direct connection to IC. The current probe does not appreciably load the crystal in this oscillator test circuit.

Figure 10 IC, in Figure 9 responds to a 1-mV input step with a gain of 1000. The 35-nsec rise time indicates the 10-MHz bandwidth. The thickened trace at the flat portions of the pulse represents the noise floor.

rent through the probe and adjusting the indicated trim for a 1V circuit output. To generate the 1 mA, drive a 1-k $\Omega$ , 0.1% resistor with 1V rms.

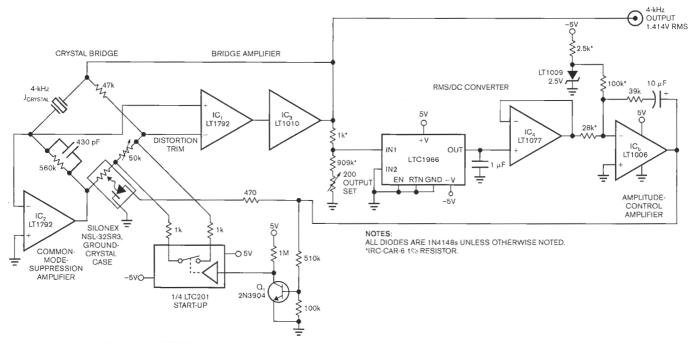

### STABLE AC-VOLTAGE STANDARD

Figure 13 uses the rms/dc converter's stability in an ac-voltage standard. Initial circuit accuracy is 0.1%, and six months of drift at 20 to 30°C remains within that figure. Additionally, the 4-kHz operating frequency is within 0.01%, and distortion is less than 30 ppm. IC<sub>1</sub> and its power buffer, IC<sub>3</sub>, sense across a bridge comprising a 4-kHz quartz crystal and an RC impedance in one arm; resistors and an LED-driven photocell comprise the other arm. IC, sees positive feedback at the crystal's 4kHz resonance, promoting oscillation. Negative feedback, stabilizing oscillation amplitude, occurs through a control path, which includes an rms/dc converter and an amplitude-control amplifier, IC5. IC5 acts on the difference between IC3's rmsconverted output and the LT1009 voltage reference. Its output controls the LED-driven photocell to set IC,'s negative feedback. RC components in IC, 's feedback path stabilize the control loop. The 50-k $\Omega$  trim sets the optically driven resistor's value to the point at which IC,'s lowest output distortion oc-

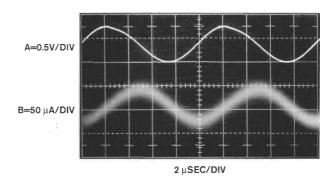

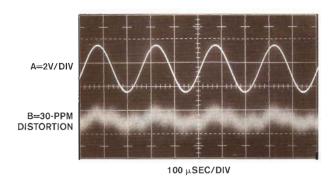

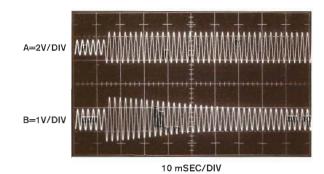

Normally, you would ground the bridge's "bottom." Although this connection works, it subjects IC, to commonmode swings, increasing distortion due to IC,'s finite commonmode rejection versus frequency. IC, eliminates this concern by forcing the bridge's midpoints and, hence, common-mode voltage to 0V but not influencing desired circuit operation. It accomplishes this task by driving the bridge bottom to force its input differential to zero. IC<sub>2</sub>'s output swing is 180° out of phase with IC<sub>3</sub>'s circuit output. This action eliminates common-mode swing at IC<sub>1</sub>, reducing circuit output distortion by more than an order of magnitude. Figure 14 shows the circuit's 1.414V-rms (2V peak) output in Trace A, and Trace B's distortion constituents include noise, fundamental-related residue, and second-harmonic components.

The 4-kHz crystal is a relatively large structure with a high Q factor. Normally, it would require more than 30 sec to start and arrive at full, regulated amplitude. You avoid this drawback by including the Q1-LTC201-switch circuitry. At startup, IC $_5$ 's output goes high, biasing Q $_1$ . Q $_1$ 's collector goes low, turning on the LTC201. This action sets IC $_1$ 's gain abnormally high, increasing bridge drive and accelerating crystal start-up. When the bridge arrives at its operating point, IC $_5$ 's output drops to a lower value, Q $_1$  and the LTC201 switch off, and the circuit moves into normal operation. Start-up time is several seconds.

The circuit requires trimming for amplitude accuracy and lowest distortion. You perform the distortion trim first. Adjust the trim for minimal output distortion, which you measure on a distortion analyzer. Note that the absolute lowest level of distortion coincides with the point at which control-loop gain is just adequate to maintain oscillation. As such, find this point and retreat from it into the control loop's active region. This retreat necessitates giving up about 5-ppm distortion, but you can achieve 30 ppm with good control-loop stability. You trim

Figure 12 Trace A shows the crystal voltage, and Trace B shows the crystal current for the circuit in Figure 11. The 25-μA rms-crystal-current measurement includes the 5-μA noise-floor contribution of the preamplifier.

output amplitude with the indicated adjustment for exactly 1.414V rms (2V peak) at the circuit output.

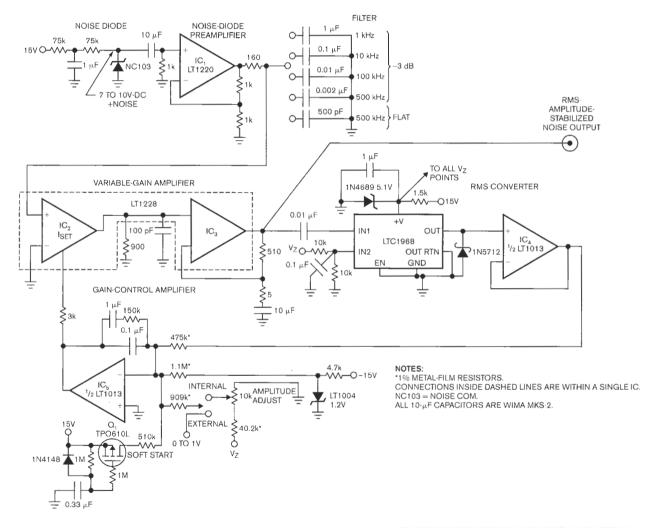

#### RANDOM-NOISE GENERATOR

Figure 15 uses the rms/dc converter in a leveled-output-random-noise generator. Noise diode  $D_1$  ac-biases  $IC_1$ , operating at a gain of two.  $IC_1$ 's output feeds a 1- to 500-kHz, switch-selectable lowpass filter. The filter output-biases the variable-gain amplifier,  $IC_2$ - $IC_3$ .  $IC_2$ , a current-controlled transconductance amplifier, and  $IC_3$ , an output amplifier, reside on one chip. This stage takes ac gain, biases the LTC1968 rms/dc converter, and acts as the circuit's output. The rms-converter output at  $IC_4$

Figure 1.1 This quartz-stabilized sine-wave-output-ac reference has 0.1% long-term amplitude stability. The frequency accuracy is 0.01% with less-than-30-ppm distortion. The positive feedback around IC, causes oscillation at the crystal's resonant frequency. Amplifier IC, acts on the rms-amplitude output of IC, to supply a negative feedback to IC, through the bridge network that stabilizes the rms-output amplitude. The optocoupler minimizes feedback-induced distortion. Switch O, closes during start-up, which ensures the rapid build up of oscillations.

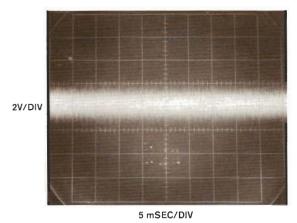

feeds back to gain-control amplifier IC<sub>5</sub>, which compares the rms value with a variable portion of the 5.1V zener potential. IC<sub>5</sub>'s output sets IC<sub>2</sub>'s gain through the 3-k $\Omega$  resistor, completing a control loop to stabilize noise-rms-output amplitude. The RC components in IC<sub>5</sub>'s local feedback path stabilize this loop. You can vary the output amplitude using the 10-k $\Omega$  potentiometer; a switch permits external voltage control. Q<sub>1</sub> and associated components, a soft-start circuit, prevent output overshoot at power turn-on. Figure 16 shows circuit-output noise in the 10-kHz filter position; Figure 17's spectral plot reveals essentially flat rms-noise amplitude over a 500-kHz bandwidth.

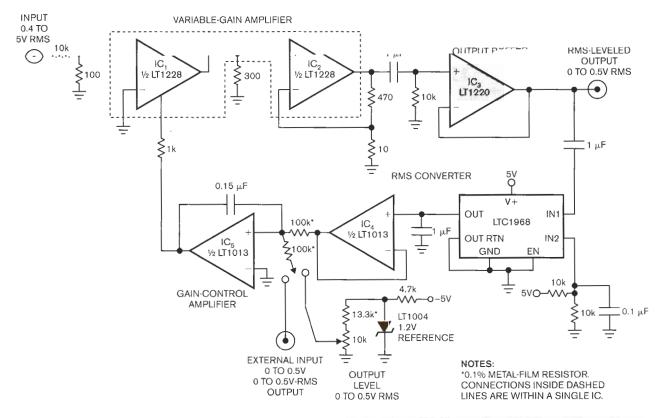

# RMS-AMPLITUDE-STABILIZED LEVEL CONTROLLER

Figure 18 borrows the previous circuit's gain-control loop to stabilize the rms amplitude of an arbitrary input waveform. You apply the unregulated input to variable-gain amplifier IC<sub>1</sub>-IC<sub>2</sub> which feeds IC<sub>3</sub>. DC coupling at IC<sub>1</sub>-IC<sub>2</sub> permits passage of low-frequency inputs. An rms/dc converter, comprising IC<sub>4</sub> and IC<sub>6</sub>, takes IC<sub>3</sub>'s output, which feeds IC<sub>5</sub>'s gain-control amplifier. IC<sub>5</sub> compares the rms value with a variable reference and biases IC<sub>1</sub>,

Figure 14 Trace A shows the 1.414V-rms (2V peak) reference output from IC<sub>a</sub>. Trace B shows the 30-ppm distortion in the output. The distortion's constituents include noise, fundamental-related residue, and second-harmonic components.

Figure 15 This circuit creates a random-noise generator with rms-leveled output.  $IC_1$  filters and amplifies zener-diode noise. The output of the variable-gain amplifier converts to rms. The rms output feeds back to gain-control amplifier  $IC_5$ , which closes the loop to the variable-gain amplifier. A potentiometer or external input to  $IC_5$  allows you to set the noise output to different values.

Figure 16 The output of the circuit in Figure 14 is in the 10-kHz filter position.

closing a gain-control loop. The  $0.15-\mu F$  feedback capacitor stabilizes this loop, even for waveforms lower than 100 Hz. This feedback action maintains waveshape and stabilizes output-rms amplitude despite large variations in input amplitude. You can set the desired output level with the indicated potentiometer, or you can switch in an external control voltage.

Figure 19 shows output response (Trace B) to abrupt ref-

Figure 17 The amplitude over frequency for the random-noise generator is essentially flat to 500 kHz. The NC103 noise diode contributes to an even noise-spectrum distribution, and the rms converter and control loop stabilize the amplitude. The measurement sweep time is 2.8 minutes, and the resolution bandwidth is 100 Hz.

erence-level-setpoint changes (Trace A). The output settles within 60 msec for ascending and descending transitions. You can achieve faster response by decreasing  $IC_5$ 's compensation capacitor, but the circuit would then be unable to process low-frequency waveforms. Similar considerations apply to **Figure**

Figure 18 This rms amplitude level-control circuit uses the gain-control loop of Figure 15. The amplifiers  $IC_1$ ,  $IC_2$ , and  $IC_3$  provide a variable-gain capability to the input section. The rms converter,  $IC_6$ , feeds back to the gain-control amplifier,  $IC_6$ , which closes the amplitude-stabilization loop. The variable-reference voltage permits a settable calibrated rms output that is amplitude-independent of the input waveshape.

20 mSEC/DIV

Figure 19 An abrupt change in the reference (Trace A) causes an amplitude-level-control response (Trace B). IC<sub>s</sub>'s compensation capacitor sets the settling time. This capacitor must be large enough to stabilize the loop at the lowest expected signal-input frequency.

20's response to an input-waveform step change. Trace A is the circuit's input, and Trace B is its output. The output settles in 60 msec due to IC<sub>5</sub>'s compensation. Reducing compensation value speeds response at the expense of low-frequency-waveform processing capability. Specifications include 0.1% output-amplitude stability for inputs of 0.4 to 5V rms, 1% setpoint accuracy, 0.1- to 500-kHz passband, and 0.1% stability for 20% power-supply deviation. EDN

# REFERENCES

1 "1968 Instrumentation/Electronic-Analytical-Medical," AC

Figure 20 The amplitude-level-control output (Trace B) reacts to a step change in the input signal (Trace A). The slow loop compensation allows the overshoot, but the output settles cleanly.

Voltage Measurement, Hewlett-Packard Co, 1968, pg 197.

- Sheingold, DH, editor, Nonlinear Circuits Handbook, Second Edition, Analog Devices Inc., 1976.

- Model LK-343A-FM Manual, Lambda Electronics.

- Grafham, DR, "Using Low Current SCRs," General Electric AN200.19, January 1967.

- Williams, Jim, "Performance Enhancement Techniques for Three-Terminal Regulators—SCR Preregulator," Linear Technology Corp. AN-2, pg 3, August 1984.

- Milliams, Jim, "High Efficiency Linear Regulators—SCR Preregulator," Linear Technology Corp, Application Mote 32, March 1989, pg 3.

- Williams, Jim, "High Speed Amplifier Techniques—Parallel Path Amplifiers," Linear Technology Corp, Application Note 47,

August 1991, pg 35.

- Milliams, Jim, "Practical Circuitry for Measurement and Control Problems," "Broadband Random Noise Generator," "Symmetrical White Gaussian Noise," Appendix B, Linear Technology Corp, Application Note 61, August 1994, pg 24 and 38.

- Williams, Jim, "A Fourth Generation of LCD Backlight Technology," "rms Voltmeters," Linear Technology Corp, Application Note 65, November 1995, pg 82.

- Meacham, LA, "The Bridge Stabilized Oscillator," Bell System Technical Journal, Volume 17, October 1938, pg 574.

- Williams, Jim, "Bridge Circuits— Marrying Gain and Balance," Linear Technology Corp, Application Note 43, June 1990.

# AUTHOR'S BIOGRAPHY

Long-time EDN contributor Jim Williams, staff scientist at Linear Technology Corp (Milpitas, CA), has more than 40 years' experience in analog-circuit and instrumentation design.

Email:DCDC@delta-corp.com Fax:(978)656-3964